# 晟矽微电 8 位单片机

# MC32F8152

# 用户手册

V1.0.4

# 目录

| 1 | 产品    | 概要          | 5  |

|---|-------|-------------|----|

|   | 1.1   | 产品特性        | 5  |

|   | 1.2   | 订购信息        | 7  |

|   | 1.3   | 引脚排列        | 8  |

|   | 1.4   | 端口说明        | 13 |

| 2 | 电气    | 特性          | 14 |

|   | 2.1   | 极限参数        | 14 |

|   | 2.2   | 直流电气特性      | 14 |

|   | 2.3   | 交流电气特性      | 15 |

|   | 2.4   | PFRC 特性参数   | 16 |

|   | 2.5   | ADC 特性参数    | 16 |

|   | 2.6   | CMP 特性参数    | 17 |

|   | 2.7   | EEPROM 特性参数 | 17 |

| 3 | CPU   | 与存储器        | 18 |

|   | 3.1   | 指令集         | 18 |

|   | 3.2   | 程序存储器       | 20 |

|   | 3.3   | 数据存储器       | 21 |

|   | 3.4   | 堆栈          | 23 |

|   | 3.5   | 控制寄存器       |    |

|   | 3.6   | 用户配置字       | 27 |

| 4 | 系统    | 时钟          | 29 |

|   | 4.1   | 内部高频 RC 振荡器 | 29 |

|   | 4.2   | 内部低频 RC 振荡器 | 29 |

|   | 4.3   | 系统工作模式      | 30 |

|   | 4.4   | 低功耗模式       | 32 |

| 5 | 复位    |             | 33 |

|   | 5.1   | 复位条件        | 33 |

|   | 5.2   | 上电复位        | 33 |

|   | 5.3   | 外部复位        | 34 |

|   | 5.4   | 低电压复位       | 34 |

|   | 5.5   | 看门狗复位       | 34 |

| 6 | I/O 站 | 端口          | 35 |

|    | 6.1  | 通用 I/O 功能        | 35 |

|----|------|------------------|----|

|    | 6.2  | 内部上/下拉电阻         | 36 |

|    | 6.3  | 端口模式控制           | 38 |

|    | 6.4  | 端口驱动控制           | 39 |

| 7  | 可编程  | 程 RC 振荡器 PFRC    | 41 |

| 8  | 定时器  | 引MER             | 43 |

|    | 8.1  | 看门狗定时器 WDT       | 43 |

|    | 8.2  | 定时器 T0           | 43 |

|    | 8.3  | 定时器 T1           | 45 |

|    | 8.4  | 定时器 T2           | 48 |

|    | 8.5  | 定时器 T3           | 55 |

| 9  | 模数转  | 5换器 ADC          | 60 |

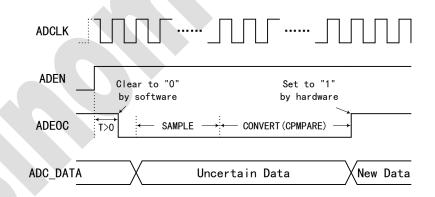

|    | 9.1  | ADC 概述           | 60 |

|    | 9.2  | ADC 相关寄存器        | 61 |

|    | 9.3  | ADC 操作步骤         |    |

|    | 9.4  | ADC 零点偏移修调流程     | 65 |

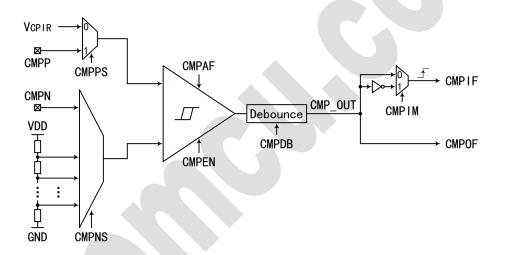

| 10 | 比较器  | 号 CMP 和低电压检测 LVD | 66 |

|    | 10.1 | CMP 概述           | 66 |

|    | 10.2 | CMP 相关寄存器        | 67 |

| 11 | 触摸接  | 安键模块 TKM         | 70 |

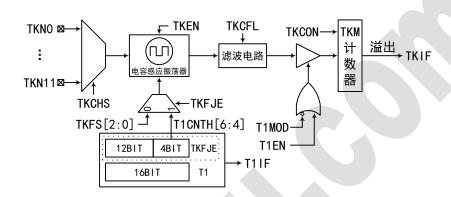

|    | 11.1 | TKM 概述           | 70 |

|    | 11.2 | TKM 相关寄存器        | 70 |

|    | 11.3 | TKM 操作步骤         | 76 |

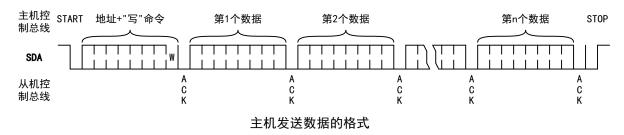

| 12 | 总线追  | 值讯 IIC           | 77 |

|    | 12.1 | IIC 概述           | 77 |

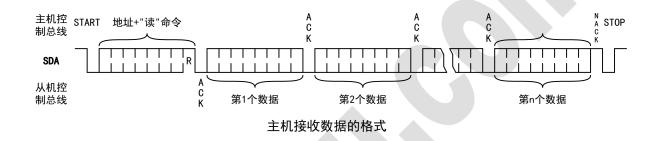

|    | 12.2 | IIC 数据传输         | 77 |

|    | 12.3 | IIC 工作模式         | 78 |

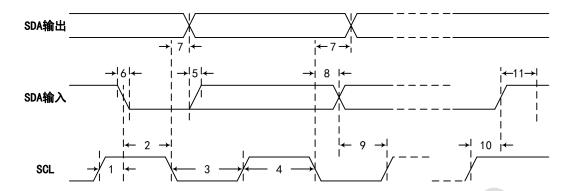

|    | 12.4 | IIC 时序说明         | 79 |

|    | 12.5 | IIC 多机通讯         | 81 |

|    | 12.6 | IIC 相关寄存器        | 81 |

| 13 | 异步道  | 通讯 UART          | 86 |

|    | 13.1 | UART 概述          | 86 |

|    | 13.2 | UART 工作模式与传输格式   | 87 |

|    | 13.3 | UART 波特率         | 87 |

|    |      |                  |    |

|    | 13.4 | UART 多机通讯              | 88  |

|----|------|------------------------|-----|

|    | 13.5 | UART 相关寄存器             | 90  |

| 14 | EEPR | OM 存储器                 | 96  |

|    | 14.1 | EEPROM 概述              | 96  |

|    | 14.2 | EEPROM 相关寄存器           | 96  |

|    | 14.3 | EEPROM 操作示例            | 97  |

| 15 |      | Ⅰ 烧录编程                 |     |

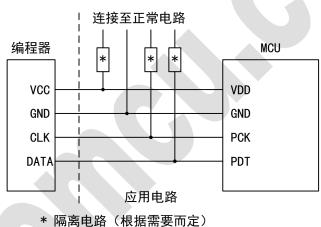

|    | 15.1 | FLASH 在板编程             | 99  |

| 16 | 中断   |                        | 102 |

|    | 16.1 | 外部中断                   | 102 |

|    | 16.2 | 定时器中断                  | 102 |

|    | 16.3 | 键盘中断                   | 103 |

|    | 16.4 | TKM 计数中断               | 103 |

|    | 16.5 | ADC 中断                 |     |

|    | 16.6 | CMP 中断                 |     |

|    | 16.7 | IIC 中断                 |     |

|    | 16.8 | UART 中断                |     |

|    | 16.9 | 中断相关寄存器                | 104 |

| 17 |      | 由线                     |     |

|    | 17.1 | I/O 特性                 |     |

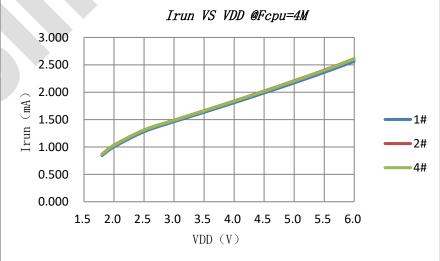

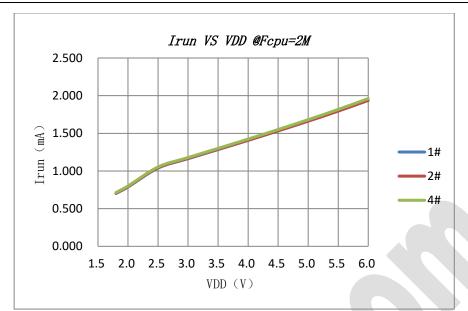

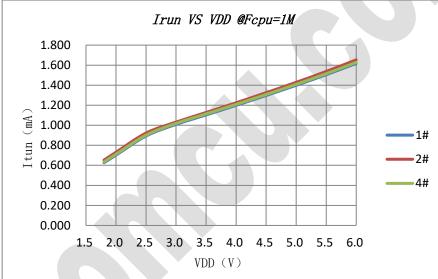

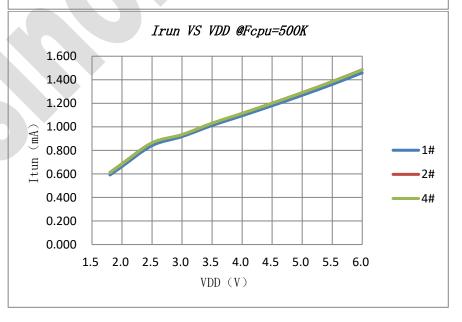

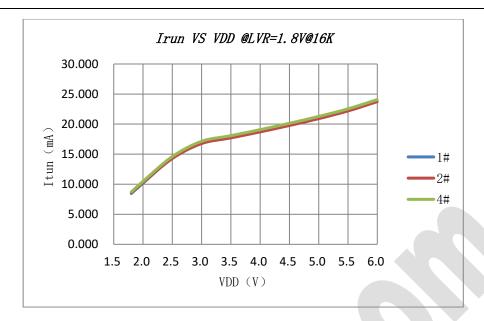

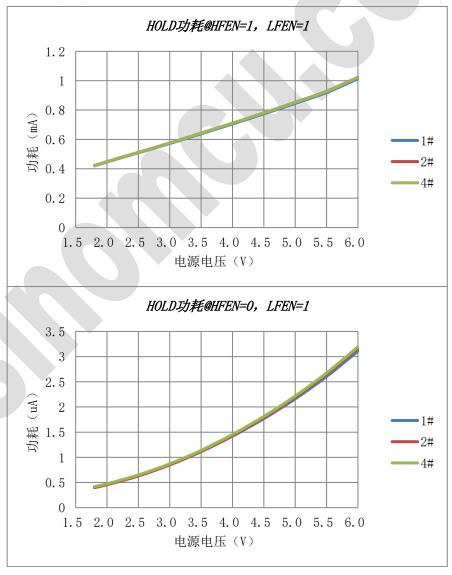

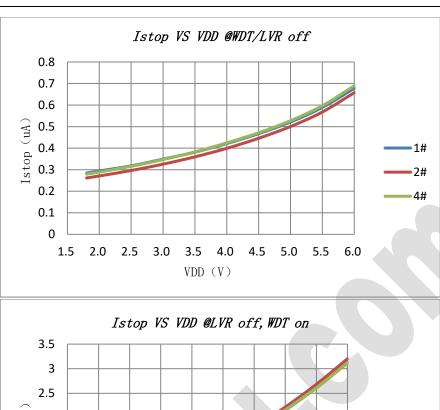

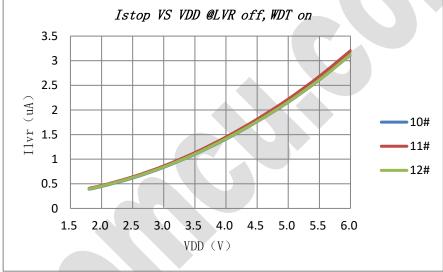

|    | 17.2 | 功耗特性                   | 115 |

|    | 17.3 | 模拟电路特性                 | 118 |

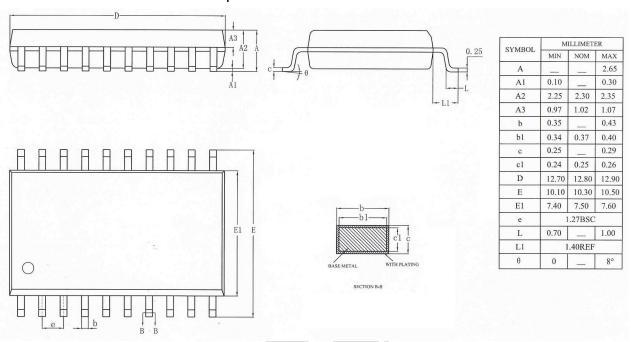

| 18 | 封装户  | 7寸                     | 124 |

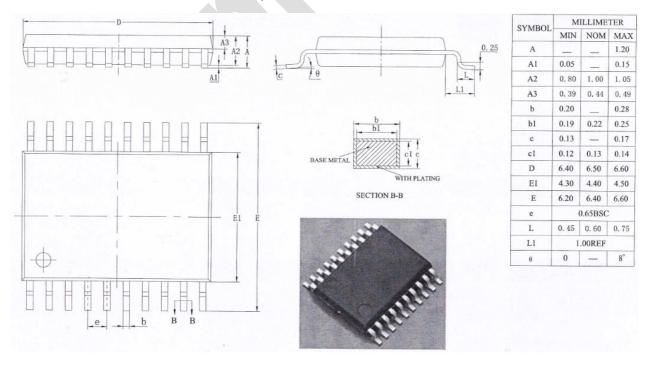

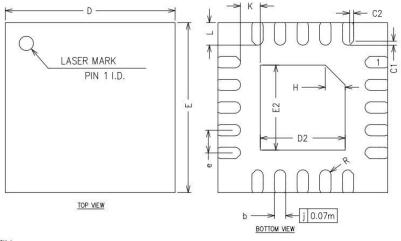

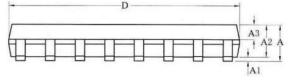

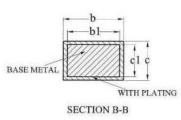

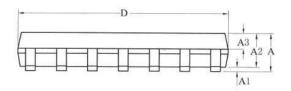

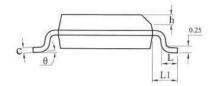

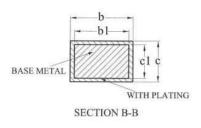

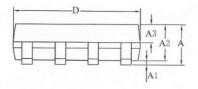

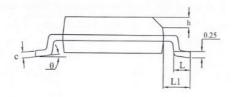

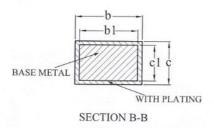

|    | 18.1 | SOP20 (1.27mm pitch)   | 124 |

|    | 18.2 | TSSOP20 (0.65mm pitch) | 124 |

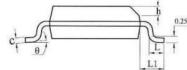

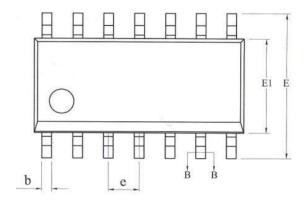

|    | 18.3 | SOP16 (1.27mm pitch)   | 125 |

|    | 18.4 | SOP14 (1.27mm pitch)   | 125 |

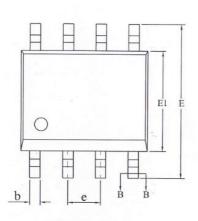

|    | 18.5 | SOP8 (1.27mm pitch)    | 126 |

| 19 | 修订证  | ᄀ录                     | 127 |

### 1 产品概要

### 1.1 产品特性

#### ■ 8 位 CPU 内核

- ◇ 精简指令集,8级深度硬件堆栈

- ◆ CPU 为双时钟,可在系统高/低频时钟之间切换

- ◆ 系统高频时钟下 FCPU 可配置为 FHOSC 的 2/4/8/16/32/64 分频

- ◆ 系统低频时钟下 FCPU 固定为 FLOSC 的 2 分频

#### ■ 程序存储器

- ◆ 4K×16 位 FLASH 型程序存储器,可通过间接寻址读取程序存储器内容

- ◆ 支持在板带电烧录编程,擦写次数至少1000次

### ■ 数据存储器

- ◆ 256 字节 SRAM 型通用数据存储器,支持直接寻址、间接寻址等多种寻址方式

- ◆ 128 字节 EEPROM 型数据存储器,支持单独烧录和软件读写,擦写次数至少 10000 次

### ■ 3组共18个I/O

- ♦ P0 (P00~P07), P1 (P10~P17), P2 (P20~P21)

- ◇ 所有端口均支持施密特输入,均支持推挽输出, P14/P15 可选推挽或开漏输出

- ◆ P14 可复用为外部复位 RST 输入, P01/P02 或 P16/P17 复用为 IIC 接口时为开漏输出

- ◇ 所有端口均内置上拉和下拉电阻,均可单独使能

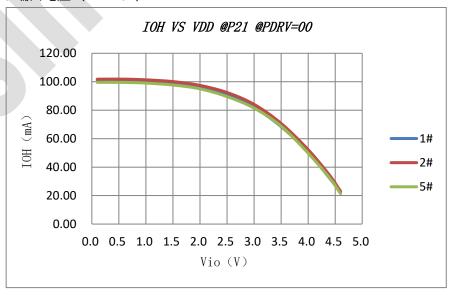

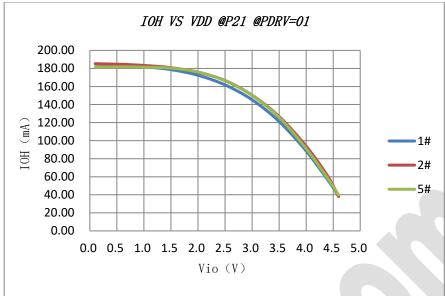

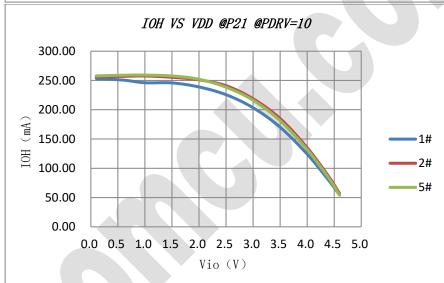

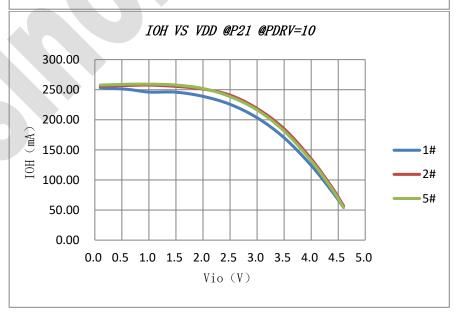

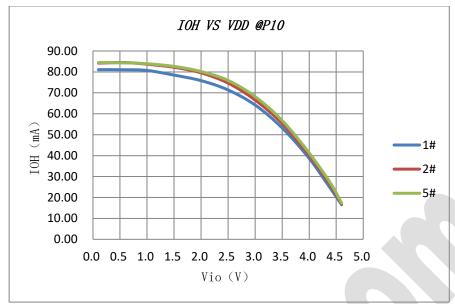

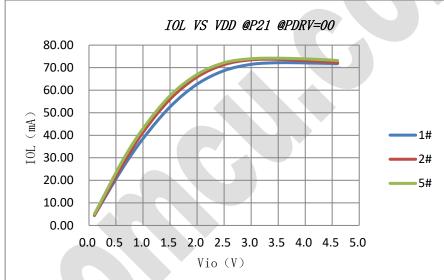

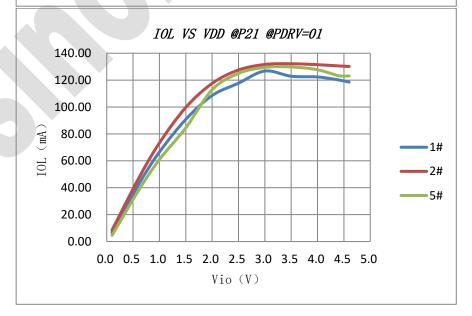

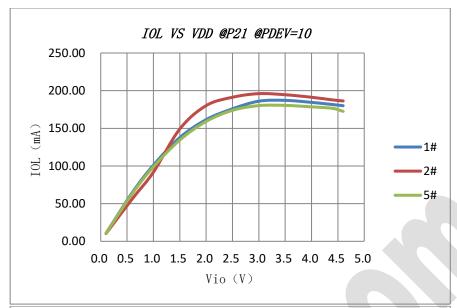

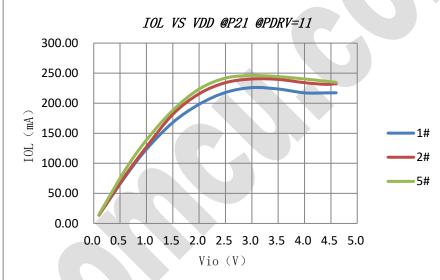

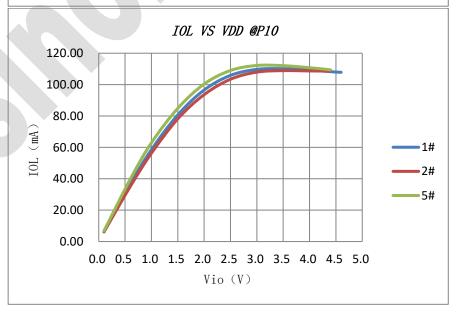

- → P20/P21 为大电流端口且输出电流 4 级(25mA/50mA/75mA/100mA)可选

- ◆ P14/P15 可复用为外部中断输入,支持外部中断唤醒功能

- ◆ P0 所有端口均支持键盘中断唤醒功能,并可单独使能

### ■ 系统时钟源

- ◆ 内置高频 RC 振荡器 (32MHz),可用作系统高频时钟源

- ◆ 内置低频 RC 振荡器 (32KHz), 可用作系统低频时钟源

#### ■ 系统工作模式

- ◆ 高速模式: CPU 在高频时钟下运行,低频时钟源工作

- ◆ 低速模式: CPU 在低频时钟下运行,高频时钟源可选停止或工作

- ◆ HOLD1 模式(低功耗模式): CPU 暂停,高频时钟源工作,低频时钟源可选停止或工作

- ◆ HOLD2 模式(低功耗模式): CPU 暂停,高频时钟源停止,低频时钟源工作

- ◇ 休眠模式(低功耗模式): CPU 暂停,高/低频时钟源均停止

- 内部自振式看门狗计数器(WDT)

- ◆ 溢出时间可配置: 16ms/64ms/256ms/1024ms

*晟矽微电* 5/127

- ◇ 工作模式可配置:始终开启、始终关闭、低功耗模式下关闭

- 4 个定时器

- ◆ 8 位定时器 T0,可实现外部计数功能

- ◇ 16 位定时器 T1,可实现外部计数功能,支持单次计时模式可用于触摸按键检测

- ◆ 8 位定时器 T2,可实现 1 对 8+3 模式的带死区互补 PWM,支持 CMP 输出信号 CMP\_OUT 高/低电平的输出保护功能

- ◆ 8 位定时器 T3,可实现 3 路共周期独立占空比的 PWM

- 1个频率可编程 RC 振荡器 PFRC

- ◆ 振荡频率初始值: 32MHz

- ◆ 12 位微调校准位,微调精度±0.2%

- ◆ 最大调节范围(以实际芯片为准):(32MHz-10%)~(32MHz+4%)

- ◆ 输出时钟 FPFRC 仅可用作定时器 T2/T3 的时钟源

- 1 个 12 位高精度 SAR 型 ADC

- ♦ 12 路外部通道: ANO~AN11; 4 路内部通道: GND、VDD/4、EVN0/4、EVN1/4

- ◆ ADC 时钟: FHIRC 的 32/64/128/256 分频

- ◆ 支持零点校准

- 1 个模拟比较器 CMP

- ◆ 输入共模 0~ (VDD-1.4V),输出可选有/无回滞(单边 6%)且支持去抖处理

- ◆ 正端输入可选择外部输入电压、或内部基准电压 VCPIR (0.5V)

- ◆ 负端输入可选择外部输入电压、或 VDD 内部分压电压

- ◇ 输出端电平可选择上升沿或下降沿触发中断

- ◆ 可实现输出信号 CMP\_OUT 高/低电平关闭定时器 T2 输出 PWM/FPWM 的功能

- ◆ 可实现 VDD 的低电压检测(LVD)功能

- 1个触摸按键模块 TKM

- ♦ 12 路触摸按键输入(TKN0~TKN11)

- 1组总线通讯 IIC 主从接口

- ◆ 支持7位地址编码的主机/从机模式,从机模式支持2组地址编码及广播地址(00H)编码

- ◇ 通讯速率最高支持 400Kbps

- ◇ 地址匹配、接收完成、发送完成等事件发生时,可触发中断

- ◇ 支持多主机时钟同步和总线仲裁

- ◆ 2组端口 SCL0/SDA0 或 SCL1/SDA1 可选

- 1组异步通讯 UART 接口

- ◆ 支持双线异步全双工、单线异步半双工等多种工作模式

*晟矽微电* 6/127

- ◆ 支持8位/9位数据位(含校验位)、1位/2位停止位等多种传输格式

- ◆ 内置波特率发生器,时钟源为系统高频时钟 FHOSC

- ◆ 内置接收缓冲器和锁存寄存器、发送缓冲器和移位寄存器,支持收/发数据的2级缓存

- ◇ 发送缓冲器空、接收完成、发送完成时触发中断

- ◆ 双线模式 2 组端口 RX0/TX0 或 RX1/TX1 可选,单线模式 4 路端口可选

- ◇ 支持端口电平反向输入/输出

### ■ 中断

- ♦ 外部中断 (INT0~INT1), 键盘中断 (P00~P07)

- ◇ 定时器中断(T0~T3),TKM 计数中断

- ◆ ADC 中断, CMP (LVD) 中断

- ◆ IIC 中断, UART 中断(接收完成中断、发送完成中断、发送缓冲器空中断)

### ■ 低电压检测 LVD

- ♦ 1.8V/2.0V/2.1V/2.2V/2.4V/2.5V/2.6V/2.7V/2.8V/3.0V/3.2V/3.3V/3.6V/4.0V/4.2V

- ◆ 可选择 CMPN 输入电压与内部基准电压 Vcpir (0.5V) 比较

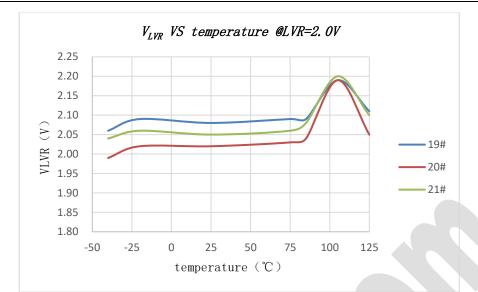

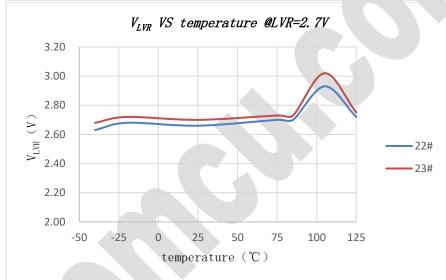

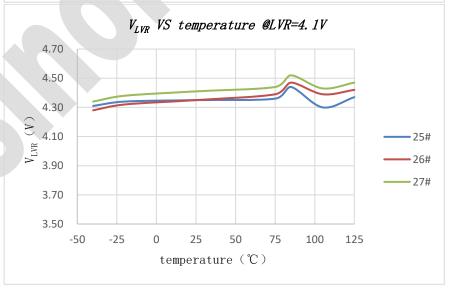

#### ■ 低电压复位 LVR

### ■ 工作电压

- $\diamond$  VLVR41 ~ 5.5V @ Fcpu = 0~16MHz

- $\Rightarrow$  VLVR27 ~ 5.5V @ Fcpu = 0~8MHz

- $\diamond$  VLVR20 ~ 5.5V @ Fcpu = 0~4MHz

- $\Rightarrow$  VLVR18 ~ 5.5V @ Fcpu = 0~1MHz

#### ■ 封装形式

♦ SOP20/QFN20/SOP16/SOP14/SOP8

### 1.2 订购信息

| 产品名称         | 封装形式  | 备注 |

|--------------|-------|----|

| MC32F8152A0M | SOP20 |    |

| MC32F8152A1M | SOP20 |    |

| MC32F8152A2M | SOP20 |    |

| MC32F8152A3M | SOP20 |    |

*晟矽微电* 7/127

| MC32F8152A0Y  | TSSOP20 | 引脚排列同 A0M |

|---------------|---------|-----------|

| MC32F8152A0ZQ | QFN20   | 3x3x0.75  |

| MC32F8152A0K  | SOP16   |           |

| MC32F8152A1K  | SOP16   |           |

| MC32F8152A2K  | SOP16   |           |

| MC32F8152A3K  | SOP16   |           |

| MC32F8152A4K  | SOP16   |           |

| MC32F8152A0J  | SOP14   |           |

| MC32F8152A0H  | SOP8    |           |

| MC32F8152A1H  | SOP8    |           |

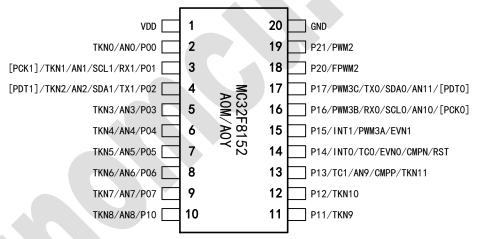

### 1.3 引脚排列

### MC32F8152A0M/A0Y

S0P20/TSS0P20

*晟矽微电* 8/127

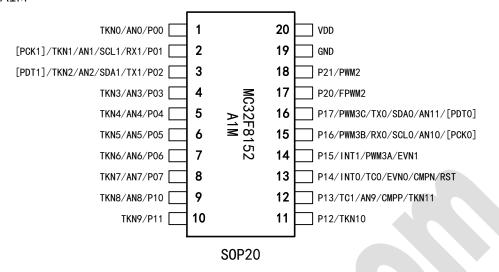

#### MC32F8152A1M

#### MC32F8152A2M

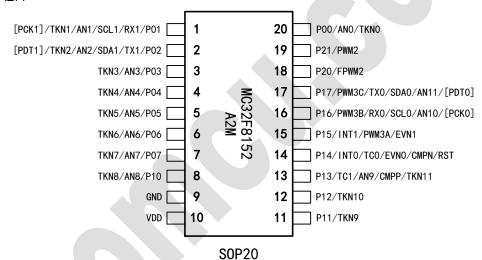

### MC32F8152A3M

晨矽微电 9/127

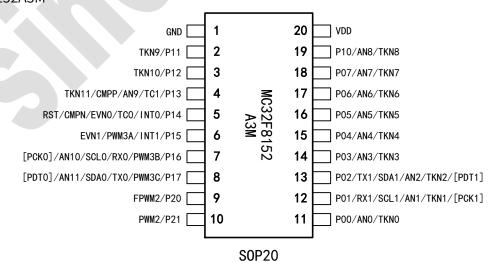

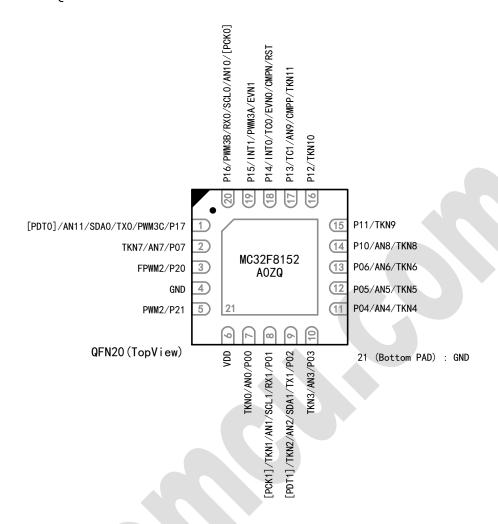

### MC32F8152A0ZQ

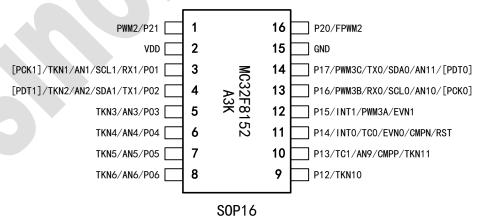

### MC32F8152A0K

*晟矽微电* 10/127

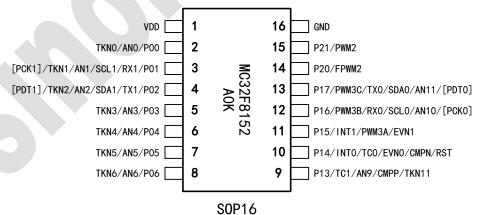

### MC32F8152A1K

#### MC32F8152A2K

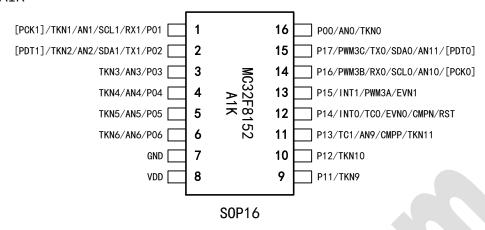

#### MC32F8152A3K

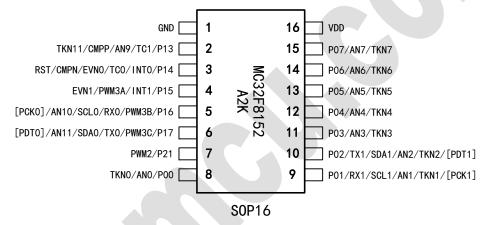

*晟矽微电* 11/127

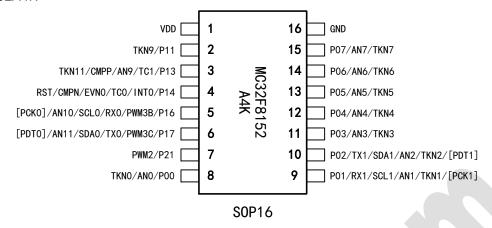

### MC32F8152A4K

#### MC32F8152A0J

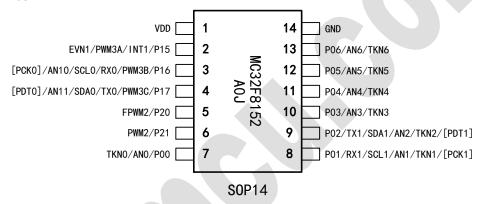

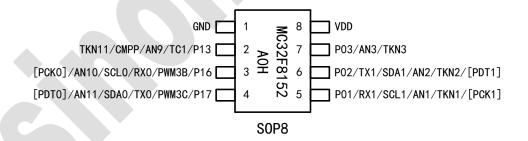

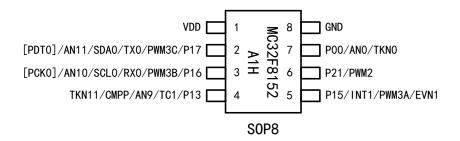

#### MC32F8152A0H

MC32F8152A1H

晟砂微电

### 1.4 端口说明

| 端口名称                  | 类型 | 功能说明                   |

|-----------------------|----|------------------------|

| VDD                   | Р  | 电源                     |

| GND                   | Р  | 地                      |

| P0, P1(除 P14,P15), P2 | D  | GPIO(推挽输出),内部上/下拉      |

| P14, P15              | D  | GPIO(推挽输出或开漏输出),内部上/下拉 |

| INT0~INT1             | DI | 外部中断输入                 |

| TC0~TC1               | DI | 定时器 T0~T1 的外部计数输入      |

| PWM2, FPWM2           | DO | 定时器 T2 的 PWM 及其互补输出    |

| PWM3A~PWM3C           | DO | 定时器 T3 的 3 路 PWM 输出    |

| AN0~AN11              | AI | ADC 外部输入通道             |

| EVN0~EVN1             | AI | ADC 内部 1/4 分压输入通道      |

| CMPP, CMPN            | Al | CMP 正/负端外部输入           |

| TKN0~TKN11            | AI | 触摸按键输入通道               |

| SCL0/SDA0, SCL1/SDA1  | D  | IIC 通讯时钟/数据端口,开漏输出     |

| RX0/TX0, RX1/TX1      | D  | UART 通讯接收/发送端口         |

| RST                   | DI | 外部复位输入                 |

| PCK0/PDT0, PCK1/PDT1  | D  | 编程时钟/数据接口              |

注: P-电源端口; D-数字端口, DI-数字输入, DO-数字输出; A-模拟端口, AI-模拟输入, AO-模拟输出。

*晟矽微电* 13/127

## 2 电气特性

### 2.1 极限参数

| 参数                     | 符号         | 值            | 单位 |

|------------------------|------------|--------------|----|

| 电源电压                   | VDD        | -0.3~6.0     | V  |

| I/O 输入电压               | Vin        | -0.3~VDD+0.3 | V  |

| 工作温度                   | Та         | -40~85       | °C |

| 储存温度                   | Tstg       | -65~150      | °C |

| 流入 VDD 最大电流(除 P20,P21) | IVDDmax    | 50           | mA |

| 流出 GND 最大电流(除 P20,P21) | IGNDmax    | 50           | mA |

| 流过 P20,P21 最大电流        | IP20P21max | 120          | mA |

注:若芯片工作条件超过极限值,则将造成永久性损坏;若芯片长时间工作在极限条件下,则将影响其可靠性。

### 2.2 直流电气特性

VDD=5V, T=25°C

| 特性         | 符号    | 端口         | 条件                            | 最小     | 典型   | 最大   | 单位       |  |  |        |   |

|------------|-------|------------|-------------------------------|--------|------|------|----------|--|--|--------|---|

|            |       |            | Fcpu=16MHz@Fhirc/2            | VLVR41 |      | 5.5  |          |  |  |        |   |

|            |       |            | Fcpu=8MHz@Fhirc/4             | VLVR27 |      | 5.5  |          |  |  |        |   |

|            |       |            | Fcpu=4MHz@Fhirc/8             | VLVR20 |      | 5.5  |          |  |  |        |   |

| 工作电压       | VDD   | VDD        | Fcpu=2MHz@Fhirc/16            | VLVR20 |      | 5.5  | V        |  |  |        |   |

|            |       |            | Fcpu=1MHz@Fhirc/32            | VLVR18 |      | 5.5  |          |  |  |        |   |

|            |       |            | Fcpu=500KHz@Fhirc/64          | VLVR18 |      | 5.5  |          |  |  |        |   |

|            |       |            | Fcpu=16KHz@FLIRC/2            | VLVR18 |      | 5.5  |          |  |  |        |   |

| 输入漏电流      | Ileak | 所有输入脚      | VDD=5V                        | -1     |      | 1    | μΑ       |  |  |        |   |

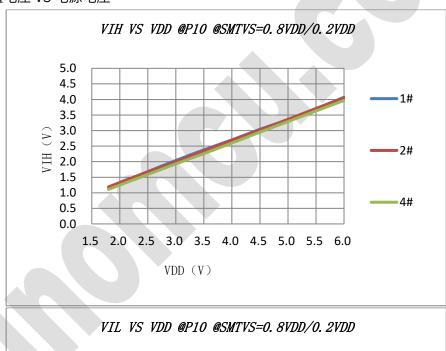

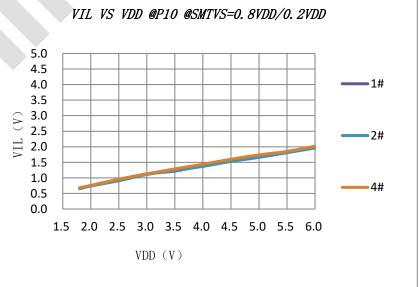

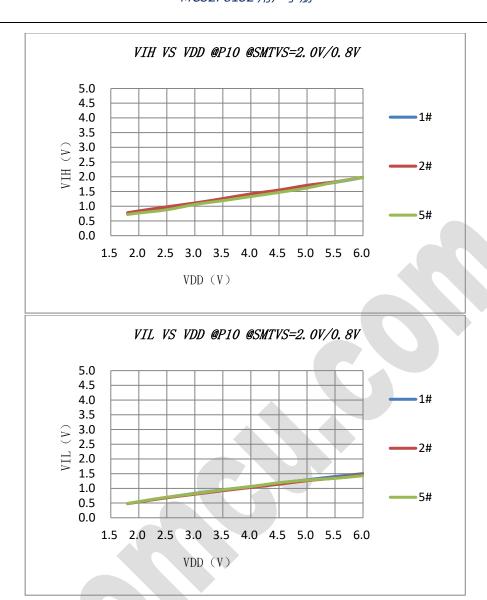

| 松)京中亚      | Vih   | 所有输入脚      | SMTVS 配置                      | 0.8VDD |      |      | . v      |  |  |        |   |

| 输入高电平      |       |            | SMTVS 配置                      | 2.0    |      |      | V        |  |  |        |   |

| 松)低电亚      | \ e1  | \ e1       | \ e1                          | \ r!   | \ r! | ᄄᆂᄾ  | SMTVS 配置 |  |  | 0.2VDD | M |

| 输入低电平      | Vil   | 'il 所有输入脚  | SMTVS 配置                      |        |      | 0.8  | V        |  |  |        |   |

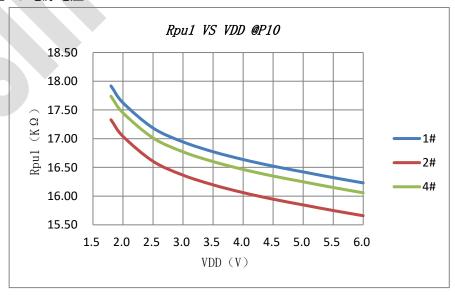

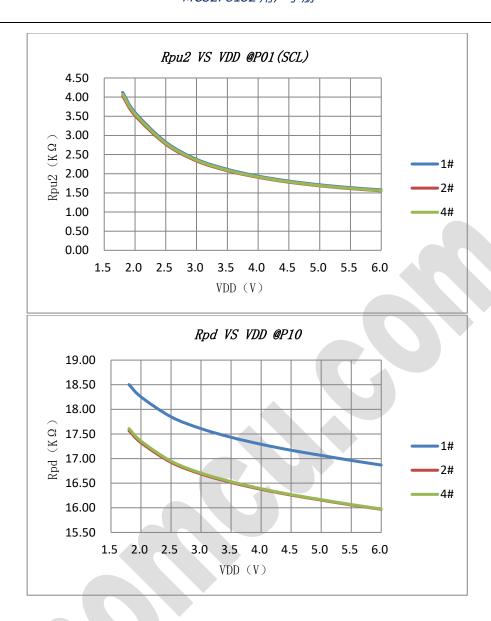

| L +÷ ch 70 | Rpu1  | P0, P1, P2 | VDD=5V, Vin=0                 | -25%   | 20   | +25% | ΚΩ       |  |  |        |   |

| 上拉电阻       | Rpu2  | SCL/SDA    | VDD=2.4V~5.5V,Vin=0, IIC 专用上拉 |        | 3    |      | ΚΩ       |  |  |        |   |

| 下拉电阻       | Rpd   | P0, P1, P2 | Vin=VDD=5V                    | -25%   | 20   | +25% | ΚΩ       |  |  |        |   |

| 输出源电流      | loh1  | P20,P21    | Voh=VDD-0.6V, PDRV=00         |        | 25   |      | mA       |  |  |        |   |

*晟矽微电* 14/127

|                |        |             |                       |      |     |      | _   |

|----------------|--------|-------------|-----------------------|------|-----|------|-----|

|                |        |             | Voh=VDD-0.6V, PDRV=01 |      | 50  |      | mA  |

|                |        |             | Voh=VDD-0.6V, PDRV=10 |      | 75  |      | mA  |

|                |        |             | Voh=VDD-0.6V, PDRV=11 |      | 100 |      | mA  |

|                | Ioh2   | 其他输出脚       | Voh=VDD-0.6V          |      | 20  |      | mA  |

|                |        |             | Vol=0.6V, PDRV=00     |      | 25  |      | mA  |

|                | Iol1   | P20,P21     | Vol=0.6V, PDRV=01     |      | 50  |      | mA  |

| 输出灌电流          | 1011   | P20,P21     | Vol=0.6V, PDRV=10     |      | 75  |      | mA  |

|                |        |             | Vol=0.6V, PDRV=11     |      | 100 |      | mA  |

|                | Iol2   | 其他输出脚       | Vol=0.6V              |      | 30  |      | mA  |

| +4-11-75-11-75 |        | 推挽输出脚       | 高速输出@空载               |      |     | 16   | MHz |

| 输出驱动管          |        | (除 P20,P21) | 低速输出@空载               |      |     | 2    | MHz |

| 开关速度           |        | P20, P21    | 带载 1000pF             |      |     | 4    | MHz |

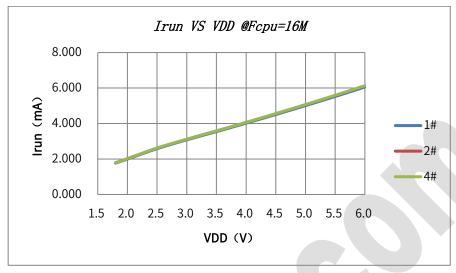

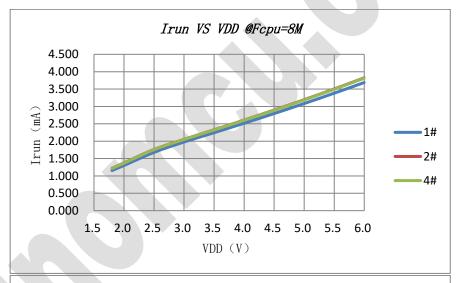

|                | Irun   |             | Fcpu=16MHz@HIRC       |      | 5.0 |      | mA  |

|                |        | VDD         | Fcpu=8MHz@HIRC        |      | 3.2 |      | mA  |

|                |        |             | Fcpu=4MHz@HIRC        |      | 2.2 |      | mA  |

| 运行模式功耗         |        |             | Fcpu=2MHz@HIRC        |      | 1.7 |      | mA  |

|                |        |             | Fcpu=1MHz@HIRC        |      | 1.5 |      | mA  |

|                |        |             | Fcpu=500KHz@HIRC      |      | 1.3 |      | mA  |

|                |        |             | Fcpu=32KHz/2@LIRC     |      | 22  |      | μΑ  |

| HOLD1 功耗       | Ihold1 | VDD         | CPU 停, HIRC/LIRC 开    |      | 850 |      | μΑ  |

| HOLD2 功耗       | Ihold2 | VDD         | CPU 停, HIRC 关, LIRC 开 |      | 2.5 |      | μΑ  |

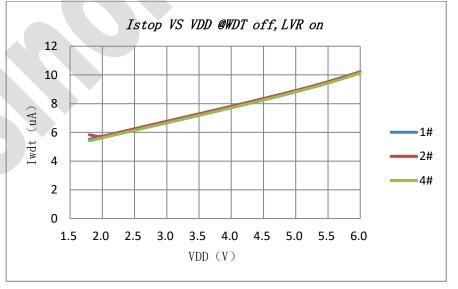

|                |        |             | 休眠模式, WDT/LVR 关       |      | 0.5 | 1    | μΑ  |

| 休眠模式功耗         | Istop  | VDD         | 休眠模式, WDT 开, LVR 关    |      | 2.5 | 5    | μΑ  |

|                |        |             | 休眠模式, WDT 关, LVR 开    |      | 9   | 20   | μΑ  |

| 低压检测电压         | VLVD   | VDD         | CMPEN=1, CMPPS=0      | -10% |     | +10% | V   |

| 低压复位电压         | VLVR   | VDD         | LVRVS 配置              | -10% |     | +10% | V   |

| LVR 回滞电压       |        | VDD         |                       |      | 6%  | 12%  |     |

注:条件项中,无关模块默认关闭,无关端口设为低电平无负载输出或内部上/下拉电阻无效且外接 GND 的输入。

### 2.3 交流电气特性

| 特性        | 符号    | 条件             | 最小    | 典型 | 最大    | 单位  |

|-----------|-------|----------------|-------|----|-------|-----|

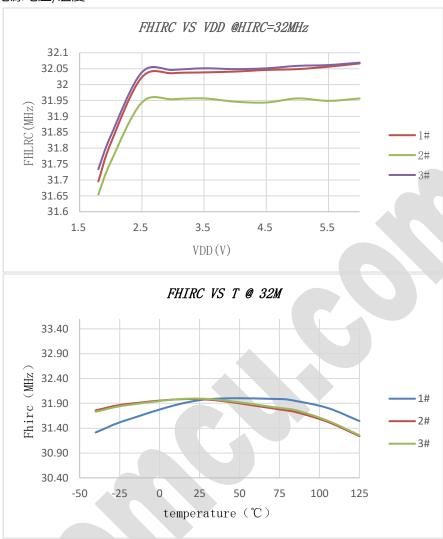

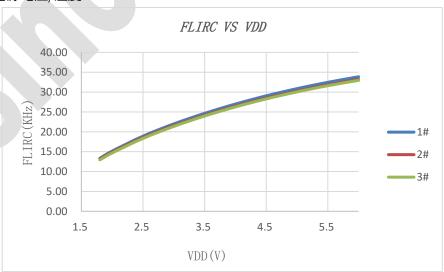

| HIRC 振荡频率 | FHIRC | VDD=5V, T=25°C | -1.5% | 32 | +1.5% | MHz |

*晟矽微电* 15/127

|           |       | VDD=2.0V~5.5V, T=-20°C~70°C | -3%  |    | +3%  |     |

|-----------|-------|-----------------------------|------|----|------|-----|

|           |       | VDD=2.0V~5.5V, T=-40°C~85°C | -5%  |    | +5%  |     |

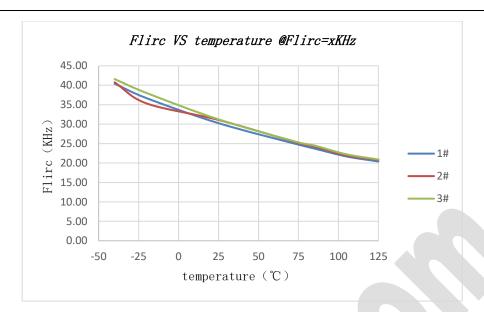

| LIRC 振荡频率 | FLIRC | VDD=5V, T=25°C              | -50% | 32 | +50% | KHz |

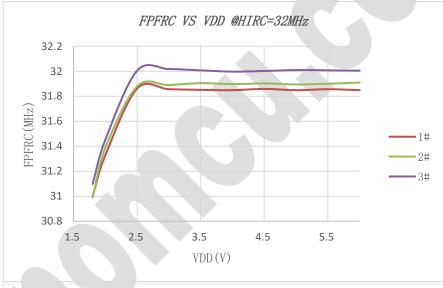

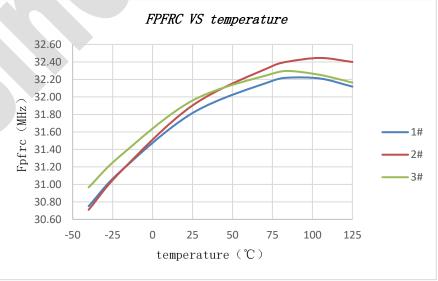

## 2.4 PFRC 特性参数

| 特性        | 符号    | 条件                          | 最小    | 典型 | 最大    | 单位  |

|-----------|-------|-----------------------------|-------|----|-------|-----|

|           |       | VDD=5V, T=25°C              | -1.5% |    | +1.5% |     |

| PFRC 振荡频率 | FPFRC | VDD=2.0V~5.5V, T=-20°C~70°C | -3%   | 32 | +3%   | MHz |

|           |       | VDD=2.0V~5.5V, T=-40°C~85°C | -5%   |    | +5%   |     |

# 2.5 ADC 特性参数

VDD=5V, T=25°C

| 特性            | 符号    | 条件                             | 最小    | 典型    | 最大         | 单位     |

|---------------|-------|--------------------------------|-------|-------|------------|--------|

| ADC 有效工作电压    | Vadc  | T=-40°C~85°C                   | 2.5   |       | 5.5        | V      |

| 积分非线性误差       | INL   | VREF=VDD, FADC=1MHz, Tcon=27µs |       |       | <u>±</u> 4 | LSB    |

| 微分非线性误差       | DNL   | VREF=VDD, FADC=1MHz, Tcon=27μs |       |       | ±2         | LSB    |

| 零点偏移误差        | EZ    | VREF=VDD, FADC=1MHz, Tcon=27μs |       |       | ±4         | LSB    |

| 增益误差          | ET    | VREF=VDD, FADC=1MHz, Tcon=27μs |       |       | ±4         | LSB    |

| 转换时钟          | FADC  | VDD=5V                         |       |       | 1          | MHz    |

| 转换时间          | Tcon  |                                | 14    |       | 27         | 1/Fadc |

| ADC 输入电压      | Vain  |                                | GND   |       | VREF       | V      |

| ADC 输入阻抗      | Rain  |                                | 2     |       |            | МΩ     |

| ADC 输入电流      | lain  |                                |       |       | 2          | μΑ     |

| ADC 动态电流      | ladd  | VDD=5V, AD 转换中                 |       | 1     | 3          | mA     |

| ADC 静态电流      | lads  | VDD=5V, ADC 关闭                 |       | 0.1   | 1          | μΑ     |

| 模拟信号源推荐阻抗     | Zain  |                                |       |       | 10         | ΚΩ     |

| 内部 1/4 分压电阻总值 | Revi  | Vin=VDD=2.5V~5.5V              |       | 24    |            | ΚΩ     |

| 电阻分压比值        |       |                                | -1%   | 1/4   | +1%        | VEVI   |

| ADC 会老中正      | \/p== | 选择 VDD                         |       | VDD   |            | V      |

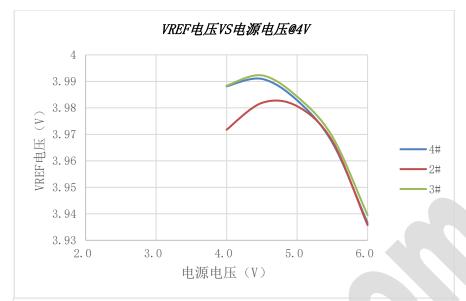

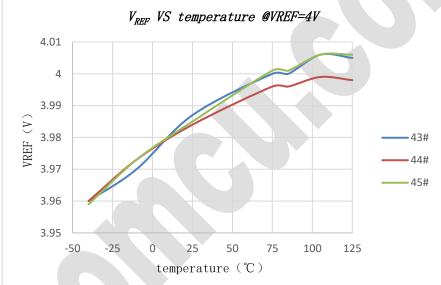

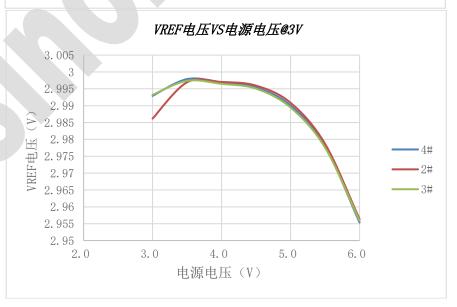

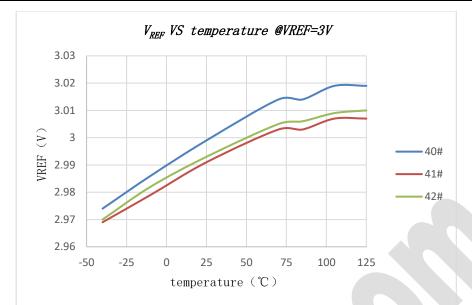

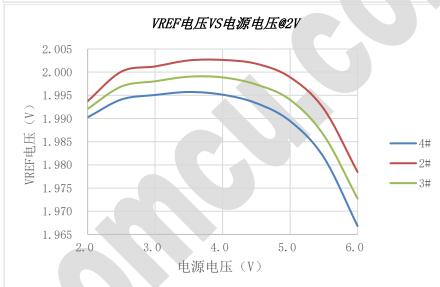

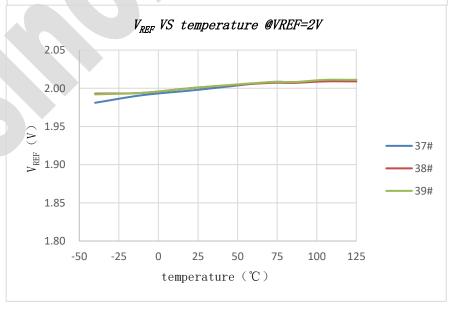

| ADC 参考电压      | VREF  | 选择内部参考电压 ViR, T=25℃            | -1.5% | 2/3/4 | +1.5%      | V      |

*晟矽微电* 16/127

|            |      | 选择内部参考电压 ViR, T=-40℃~85℃ | -3%     | +3% |   |

|------------|------|--------------------------|---------|-----|---|

| VIR 有效工作电压 | Vvir | 选择内部参考电压 VIR             | VIR+0.5 | 5.5 | V |

### 2.6 CMP 特性参数

VDD=5V, T=25°C

| 特性        | 符号      | 条件           | 最小   | 典型  | 最大      | 单位 |

|-----------|---------|--------------|------|-----|---------|----|

| 比较器有效工作电压 | Vсмр    | T=-40°C~85°C | 2.0  |     | 5.5     | V  |

| 工作电流      | Ісмр    |              |      | 10  |         | μΑ |

| 输入失调电压    | Voffset |              | -15  |     | +15     | mV |

| 输入共模电压    | Vcom    |              | 0    |     | VDD-1.4 | V  |

| 输出回滞电压    | Vhys    |              |      | 6%  | 12%     | mV |

| 响应时间      | TRESP   |              |      | 1   | 10      | μs |

| 通道切换等待时间  | Tccw    |              |      |     | 2       | μs |

| 内部基准电压    | Vcpir   |              | -10% | 0.5 | +10%    | V  |

| 电阻分压比值    |         |              | -1%  |     | +1%     |    |

### 2.7 EEPROM 特性参数

VDD=5V, T=25°C

| 特性             | 符号     | 条件                          | 最小    | 典型 | 最大  | 单位    |

|----------------|--------|-----------------------------|-------|----|-----|-------|

| EEPROM 读操作电压   | VEERD  | T=-40°C~85°C                | 2.0   |    | 5.5 | V     |

| EEPROM 写操作电压   | VEEWR  | T=-40°C~85°C                | 2.0   |    | 5.5 | V     |

| EEPROM 写操作电流   | leewr  | T=-40°C~85°C                |       | 2  |     | mA    |

| EEPROM 静态电流    | leestp | T=25°C                      |       | 1  |     | μΑ    |

| EEPROM 单地址写入时间 | TEEWR  | VDD=2.0V~5.5V, T=-40°C~85°C |       | 5  |     | ms    |

| EEPROM 擦写次数    |        | VDD=5V, T=25°C              | 10000 |    |     | cycle |

| EEPROM 数据保持时间  |        |                             | 10    |    |     | year  |

*晟矽微电* 17/127

### 3 CPU 与存储器

### 3.1 指令集

芯片的指令集为精简指令集。

除程序跳转类指令外,其他指令均为单周期指令,即执行时间为 1 个指令周期(CPU 时钟周期); 所有指令均为单字指令,即指令码仅占用 1 个程序存储器地址空间。

### 指令汇总表

| 助记符      | 说明                      | 操作                                                                        | 周期 | 长度 | 标志     |

|----------|-------------------------|---------------------------------------------------------------------------|----|----|--------|

| ADDAR R  | R 和 A 相加,结果存入 A         | R+A→A                                                                     | 1  | 1  | C,DC,Z |

| ADDRA R  | R 和 A 相加,结果存入 R         | R+A→R                                                                     | 1  | 1  | C,DC,Z |

| ADCAR R  | R 和 A 相加(带 C 标志),结果存入 A | R+A+C→A                                                                   | 1  | 1  | C,DC,Z |

| ADCRA R  | R 和 A 相加(带 C 标志),结果存入 R | R+A+C→R                                                                   | 1  | 1  | C,DC,Z |

| RSUBAR R | R和A相减,结果存入A             | R-A→A                                                                     | 1  | 1  | C,DC,Z |

| RSUBRA R | R和A相减,结果存入R             | R-A→R                                                                     | 1  | 1  | C,DC,Z |

| RSBCAR R | R和A相减(带C标志),结果存入A       | R-A-/C→A                                                                  | 1  | 1  | C,DC,Z |

| RSBCRA R | R和A相减(带C标志),结果存入R       | R-A-/C→R                                                                  | 1  | 1  | C,DC,Z |

| ASUBAR R | A 和 R 相减,结果存入 A         | A-R→A                                                                     | 1  | 1  | C,DC,Z |

| ASUBRA R | A 和 R 相减,结果存入 R         | A-R→R                                                                     | 1  | 1  | C,DC,Z |

| ASBCAR R | A 和 R 相减(带 C 标志),结果存入 A | A-R-/C→A                                                                  | 1  | 1  | C,DC,Z |

| ASBCRA R | A 和 R 相减(带 C 标志),结果存入 R | A-R-/C→R                                                                  | 1  | 1  | C,DC,Z |

| ANDAR R  | R 和 A 与操作,结果存入 A        | R and A→A                                                                 | 1  | 1  | Z      |

| ANDRA R  | R 和 A 与操作,结果存入 R        | R and A→R                                                                 | 1  | 1  | Z      |

| ORAR R   | R 和 A 或操作,结果存入 A        | R or A→A                                                                  | 1  | 1  | Z      |

| ORRA R   | R 和 A 或操作,结果存入 R        | R or A→R                                                                  | 1  | 1  | Z      |

| XORAR R  | R 和 A 异或操作,结果存入 A       | R xor A→A                                                                 | 1  | 1  | Z      |

| XORRA R  | R 和 A 异或操作,结果存入 R       | R xor A→R                                                                 | 1  | 1  | Z      |

| COMAR R  | 对 R 取反,结果存入 A           | R 取反→A                                                                    | 1  | 1  | Z      |

| COMR R   | 对 R 取反,结果存入 R           | R 取反→R                                                                    | 1  | 1  | Z      |

| RLA      | A 循环左移(带 C 标志)          | $A[7] \rightarrow C$ ; $A[6:0] \rightarrow A[7:1]$ ; $C \rightarrow A[0]$ | 1  | 1  | С      |

| RLAR R   | R 循环左移(带 C 标志),结果存入 A   | $R[7] \rightarrow C$ ; $R[6:0] \rightarrow A[7:1]$ ; $C \rightarrow A[0]$ | 1  | 1  | С      |

| RLR R    | R 循环左移(带 C 标志),结果存入 R   | $R[7] \rightarrow C$ ; $R[6:0] \rightarrow R[7:1]$ ; $C \rightarrow R[0]$ | 1  | 1  | С      |

| RRA      | A 循环右移(带 C 标志)          | $A[0] \rightarrow C$ ; $A[7:1] \rightarrow A[6:0]$ ; $C \rightarrow A[7]$ | 1  | 1  | С      |

| RRAR R   | R 循环右移(带 C 标志),结果存入 A   | $R[0] \rightarrow C; R[7:1] \rightarrow A[6:0]; C \rightarrow A[7]$       | 1  | 1  | С      |

*晟矽微电* 18/127

| RRR            | R | R 循环右移(带 C 标志),结果存入 R        | $R[0]\rightarrow C; R[7:1]\rightarrow R[6:0]; C\rightarrow R[7]$ | 1    | 1 | С      |

|----------------|---|------------------------------|------------------------------------------------------------------|------|---|--------|

| SWAPAR         |   | 交换 R 的高低半字节,结果存入 A           |                                                                  | 1    | 1 | C      |

|                |   |                              | $R[7:4] \rightarrow A[3:0]; R[3:0] \rightarrow A[7:4]$           |      |   | -      |

| SWAPR<br>MOVRA |   | 交换 R 的高低半字节,结果存入 R           | R[7:4]→R[3:0]; R[3:0]→R[7:4]<br>A→R                              | 1    | 1 | -      |

|                |   |                              |                                                                  | 1    | 1 | 7      |

| MOVAR          |   | 将R存入A                        | R→A                                                              | 1    | 1 | Z      |

| MOVR           | R | 将R存入R                        | R→R                                                              | 1    | 1 | Z      |

| CLRA           | D | 将 A 清零<br>将 R 清零             | 0→A                                                              | 1    | 1 | Z      |

| CLRR           |   |                              | 0→R                                                              | 1    | 1 | Z      |

| INCA<br>INCR   |   | A 自加 1                       | A+1→A<br>R+1→R                                                   | 1    | 1 | -<br>Z |

|                |   | R自加1                         |                                                                  |      |   |        |

|                |   | R加 1,结果存入 A                  | R+1→A                                                            | 1    | 1 | Z      |

| DECA           |   | A 自减 1                       | A-1→A                                                            | 1    | 1 | -      |

| DECAR          |   | R自减1                         | R-1→R                                                            | 1    | 1 | Z      |

| DECAR          |   | R 减 1,结果存入 A                 | R-1→A                                                            | 1 /2 | 1 | Z      |

| JZA            |   | A 自加 1: 结果为 0 则跳过下一条指令       | A+1→A: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| JZR            |   | R 自加 1: 结果为 0 则跳过下一条指令       | R+1→R: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| JZAR           |   | R 加 1,结果存入 A: 结果为 0 则跳过下一条指令 | R+1→A: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| DJZA           |   | A 自减 1: 结果为 0 则跳过下一条指令       | A-1→A: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| DJZR           |   | R 自减 1: 结果为 0 则跳过下一条指令       | R-1→R: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| DJZAR          |   | R 减 1,结果存入 A: 结果为 0 则跳过下一条指令 | R-1→A: 结果为 0 则 PC+2→PC                                           | 1/2  | 1 | -      |

| BCLR           | , | 将 R 的第 b 位清 0                | 0→R[b]                                                           | 1    | 1 | -      |

| BSET           |   | 将 R 的第 b 位置 1                | 1→R[b]                                                           | 1    | 1 | -      |

|                |   | 若 R 的第 b 位为 0,则跳过下一条指令       | 若 R[b]=0,则 PC+2→PC                                               | 1/2  | 1 | -      |

| JBSET          |   | 若 R 的第 b 位为 1,则跳过下一条指令       | 若 R[b]=1,则 PC+2→PC                                               | 1/2  | 1 | -      |

| ADDAI          |   | I 和 A 相加,结果存入 A              | I+A→A                                                            | 1    | 1 | C,DC,Z |

| ADCAI          |   | I 和 A 相加(带 C 标志),结果存入 A      | I+A+C→A                                                          | 1    | 1 | C,DC,Z |

| ISUBALI        |   | I 和 A 相减,结果存入 A              | I-A→A                                                            | 1    | 1 | C,DC,Z |

| ISBCAI I       |   | I 和 A 相减(带 C 标志),结果存入 A      | I-A-/C→A                                                         | 1    | 1 | C,DC,Z |

| ASUBAI         | l | A 和 I 相减,结果存入 A              | A-I→A                                                            | 1    | 1 | C,DC,Z |

| ASBCAI         | I | A 和 I 相减(带 C 标志),结果存入 A      | A-I-/C→A                                                         | 1    | 1 | C,DC,Z |

| ANDAI          | I | I 和 A 与操作,结果存入 A             | I and A→A                                                        | 1    | 1 | Z      |

| ORAI           | l | I 和 A 或操作,结果存入 A             | I or A→A                                                         | 1    | 1 | Z      |

| XORAI          | I | I 和 A 异或操作,结果存入 A            | I xor A→A                                                        | 1    | 1 | Z      |

| MOVAI          | I | 将I存入A                        | I→A                                                              | 1    | 1 | -      |

| CALL           | K | 子程序调用                        | PC+1→TOS; K→PC[12:0]                                             | 2    | 1 | -      |

*晟矽微电* 19/127

| GOTO K  | 无条件跳转                      | K→PC[12:0]        | 2 | 1 | -     |

|---------|----------------------------|-------------------|---|---|-------|

| RETURN  | 从子程序返回                     | TOS→PC            | 2 | 1 | -     |

| RETAI I | 从子程序返回,并将 I 存入 A           | TOS→PC; I→A       | 2 | 1 | -     |

| RETIE   | 从中断返回                      | TOS→PC; 1→GIE     | 2 | 1 | -     |

| NOP     | 空操作                        | 空操作               | 1 | 1 | -     |

| DAA     | BCD 码加法操作后,将 A 的值调整为 BCD 码 | A(HEX 码)→A(BCD 码) | 1 | 1 | С     |

| DSA     | BCD 码减法操作后,将 A 的值调整为 BCD 码 | A(HEX 码)→A(BCD 码) | 1 | 1 | -     |

| CLRWDT  | 将看门狗计数器清零                  | 0→WDTCNT          | 1 | 1 | TO,PD |

| STOP    | 进入低功耗模式                    | 0→WDTCNT; CPU 暂停  | 1 | 1 | TO,PD |

#### 注:

- 1、 A-算术逻辑单元累加器 ALU,R-数据存储器,I-立即数,K-程序存储器地址,TOS-堆栈栈顶;

- 2、 对于条件跳转类指令,若跳转条件成立,则执行时间需 2 个指令周期,否则仅需 1 个指令周期;

- 3、 禁止采用对 C,DC,Z 标志有影响的指令访问寄存器 PFLAG;

### 3.2 程序存储器

芯片的程序存储器为 FLASH 型存储器,4K×16 位的地址空间范围为 0000H~0FFFH。程序存储器 地址分配如下图所示:

| 复位起始地址(0000H)            |

|--------------------------|

| 通用程序区<br>(0001H - 0007H) |

| 中断入口地址(0008H)            |

| 通用程序区<br>(0009H - 0FFFH) |

程序存储器支持间接寻址,可通过寄存器 INDF3 访问地址为(FSR1×256+FSR0)的程序存储器内容,高 8 位将缓存于寄存器 HIBYTE,低 8 位将缓存于寄存器 A。

例如,采用间接寻址读取程序存储器 0155H 地址中内容,高 8 位存入通用数据存储器 11H 地址中,低 8 位存入通用数据存储器 10H 地址中:

MOVAI 01H

晨矽微电 20/127

MOVRA FSR1 ;将01H写入FSR1

MOVAI 55H

MOVRA FSRO ;将 55H 写入 FSR0

MOVAR INDF3 ;读取(FSR1×256+FSR0)所指地址的程序存储器中内

容

;高8位缓存于HIBYTE,低8位缓存于A

MOVRA 10H ; 将 A 中缓存的低 8 位存入通用数据存储器 10H 地址中

MOVAR HIBYTE ;读取 HIBYTE 中缓存的高 8 位

MOVRA 11H ; 高 8 位存入通用数据存储器 11H 地址中

### 3.3 数据存储器

芯片的数据存储器包括通用数据存储器 GPR(256 字节)和特殊功能寄存器 SFR,地址映射如下表所示。其中 GPR 可直接寻址或通过 INDF0/INDF2 间接寻址,SFR 可直接寻址或通过 INDF1/INDF2 间接寻址。

数据存储器还包括掉电非易失的 EEPROM 型数据存储器(128 字节),需通过 SFR 进行读写操作,详细说明请参见后续章节。

### 数据存储器区地址映射表

| 地址        | 类型  | 0/8   | 1/9      | 2/A    | 3/B     | 4/C     | 5/D     | 6/E     | 7/F   |  |  |  |  |

|-----------|-----|-------|----------|--------|---------|---------|---------|---------|-------|--|--|--|--|

| 000H-0FFH | GPR |       | 通用数据存储器区 |        |         |         |         |         |       |  |  |  |  |

| 100H-17FH | 保留  |       | 保留       |        |         |         |         |         |       |  |  |  |  |

| 180H-187H |     | INDF0 | INDF1    | INDF2  | HIBYTE  | FSR0    | FSR1    | PCL     | PFLAG |  |  |  |  |

| 188H-18FH |     | MCR   | INDF3    | INTE0  | INTF0   | OSCMR   |         | INTE1   | INTF1 |  |  |  |  |

| 190H-197H |     | IOP0  | OEP0     | PUP0   | PDP0    | IOP1    | OEP1    | PUP1    | PDP1  |  |  |  |  |

| 198H-19FH |     | IOP2  | OEP2     | PUP2   | PDP2    | P0KBCR  |         | PMOD    | DRVCR |  |  |  |  |

| 1A0H-1A7H | SFR | T0CR  | T0CNT    | T0LOAD |         |         |         | CMPCR   | CMPDB |  |  |  |  |

| 1A8H-1AFH |     | T1CR  | T1CNTH   | T1CNTL | T1LOADH | T1LOADL |         |         |       |  |  |  |  |

| 1B0H-1B7H |     | T2CR  | T2CNT    | T2LOAD | T2DATA  | PWM2CR0 | PWM2CR1 | PWM2CR2 |       |  |  |  |  |

| 1B8H-1BFH |     | T3CR  | T3CNT    | T3LOAD | T3DATA  | T3DATB  | T3DATC  | PWM3CR  |       |  |  |  |  |

| 1C0H-1C7H |     | ADCR0 | ADCR1    | ADRH   | ADRL    | OSADJCR | P0ADCR  | P1ADCR  |       |  |  |  |  |

*晟矽微电* 21/127

| 1C8H-1CFH |    | IICCR0  | IICCR1   | IICSR    | IICDR   | IICAR   | IICAAR  | IICAMR  |         |  |  |

|-----------|----|---------|----------|----------|---------|---------|---------|---------|---------|--|--|

| 1D0H-1D7H |    | URTCR0  | URTCR1   | URTCR2   | URTSR   | URTBR   | URTDR   | URTAR   | URTMR   |  |  |

| 1D8H-1DFH |    | PFRCCR  | PFRCCALH | PFRCCALL | EECR    | EEPR    | EEAR    |         | EEDR    |  |  |

| 1E0H-1E7H |    | TKCR0   | TKCR1    | TKCR2    | TKCNTH  | TKCNTL  |         |         | TKBRES  |  |  |

| 1E8H-1EFH |    | TKF0CAL | TKF1CAL  | TKF2CAL  | TKF3CAL | TKF4CAL | TKF5CAL | TKF6CAL | TKF7CAL |  |  |

| 1F0H-1F7H | 保留 |         |          | 保留       |         |         |         |         |         |  |  |

| 1F8H-1FFH | 保留 |         |          |          |         |         |         | DBGCR   | DBGPR   |  |  |

注:上表中灰色部分的存储器地址为系统保留区,禁止对其中未定义的地址进行读写操作。

#### 数据存储器寻址方式地址组成

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8           | 7      | 6 | 5 | 4 | 3 | 2        | 1                 | 0 | 寻址方式 |  |  |

|----|----|----|----|----|----|---|-------------|--------|---|---|---|---|----------|-------------------|---|------|--|--|

| /  | /  | /  | /  | /  | /  | / | 取自指令的 9 位地址 |        |   |   |   |   |          | 取自指令的 9 位地址 直接寻址7 |   |      |  |  |

| /  | /  | /  | /  | /  | /  | / | 0 FSR0      |        |   |   |   |   | 间接寻址方式 0 |                   |   |      |  |  |

| /  | /  | /  | /  | /  | /  | / | 1           | 1 FSR1 |   |   |   |   |          | 间接寻址方式 1          |   |      |  |  |

|    |    |    | FS | R1 |    |   |             | FSR0   |   |   |   |   |          | 间接寻址方式 2          |   |      |  |  |

直接寻址方式,是以指令的低 9 位为数据存储器地址,通过指令访问,寻址范围 0~1FFH。例如,采用直接寻址方式将数据 55H 写入数据存储器 010H 地址中:

MOVAI 55H

MOVRA 10H

;将 55H 写入数据存储器 10H 地址中

间接寻址方式 0,是以 FSR0 为数据存储器地址指针,通过 INDF0 访问,寻址范围 0~0FFH。例如,采用间接寻址方式 0 将数据 55H 写入数据存储器 010H 地址中:

MOVAI 10H

MOVRA FSR0

MOVAI 55H

MOVRA INDF0

;将 55H 写入 FSR0 所指地址的数据存储器中

间接寻址方式 1,是以 FSR1 为数据存储器地址指针,通过 INDF1 访问,寻址范围 100H~1FFH。例如,采用间接寻址方式 1 将数据 55H 写入数据存储器 110H 地址中:

MOVAI 10H

MOVRA FSR1

MOVAI 55H

*晟矽微电* 22/127

MOVRA INDF1

;将 55H 写入(FSR1+256)所指地址的数据存储器中

间接寻址方式 2,是以[FSR1:FSR0]为数据存储器地址指针,通过 INDF2 访问,寻址范围 0~FFFFH。例如,采用间接寻址方式 2 将数据 55H 写入数据存储器 0010H 地址中:

MOVAI 00H

MOVRA FSR1

MOVAI 10H

MOVRA FSR0

MOVAI 55H

MOVRA INDF2

; 将 55H 写入(FSR1×256+FSR0)所指地址的数据存储器

中

注:间接寻址方式 2 最大可寻址 FFFFH,但访问数据存储器中未定义的地址时,读出数据不确定,写入操作可能会更改其他地址中的内容。

### 3.4 堆栈

芯片的堆栈为 8 级深度的硬件堆栈。当 CPU 响应中断或执行子程序调用指令时,会自动将下一条指令的 PC 值压栈保存;当 CPU 执行中断返回或子程序返回指令时,会自动将栈顶内容出栈载入 PC。

### 3.5 控制寄存器

#### 数据指针寄存器 0

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| FSR0 | FSR07  | FSR06  | FSR05  | FSR04  | FSR03  | FSR02  | FSR01  | FSR00  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] FSR0[7:0] - 数据指针寄存器 0

FSRO: 间接寻址方式 0 的指针,或间接寻址方式 2、3 的指针低 8 位。

### 数据指针寄存器 1

*晟矽微电* 23/127

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| FSR1 | FSR17  | FSR16  | FSR15  | FSR14  | FSR13  | FSR12  | FSR11  | FSR10  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] FSR1[7:0] - 数据指针寄存器 1

FSR1:间接寻址方式1的指针,或间接寻址方式2、3的指针高8位。

### 间接寻址寄存器 0

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| INDF0 | INDF07 | INDF06 | INDF05 | INDF04 | INDF03 | INDF02 | INDF01 | INDF00 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | Х      | Х      | Х      | Х      | Х      | Х      | X      | Х      |

BIT[7:0] INDF0[7:0] - 间接寻址寄存器 0

INDF0: INDF0 不是物理寄存器,对 INDF0 操作实际是对 FSR0 所指向地址的数据存储器进行操作,从而实现间接寻址功能。

#### 间接寻址寄存器 1

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| INDF1 | INDF17 | INDF16 | INDF15 | INDF14 | INDF13 | INDF12 | INDF11 | INDF10 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | Х      | X      | X      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] - 间接寻址寄存器 1

INDF1: INDF1 不是物理寄存器,对 INDF1 操作实际是对(FSR1+256)所指向地址的数据存储器进行操作,从而实现间接寻址功能。

### 间接寻址寄存器 2

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| INDF2 | INDF27 | INDF26 | INDF25 | INDF24 | INDF23 | INDF22 | INDF21 | INDF20 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] INDF2[7:0] - 间接寻址寄存器 2

INDF2: INDF2 不是物理寄存器,对 INDF2 操作实际是对(FSR1×256+FSR0)所指向地址的数据存储器进行操作,从而实现间接寻址功能。

*晟矽微电* 24/127

### 间接寻址寄存器3

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| INDF3 | INDF37 | INDF36 | INDF35 | INDF34 | INDF33 | INDF32 | INDF31 | INDF30 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] INDF3[7:0] - 间接寻址寄存器 3

INDF3: INDF3 不是物理寄存器,对 INDF3 操作实际是对(FSR1×256+FSR0)所指向地址的程序存储器进行操作,从而实现间接寻址功能。

注:对寄存器 INDF3 仅可执行读取操作,且仅可使用读取指令(MOVAR INDF3),所读程序存储器内容的高 8 位存入寄存器 HIBYTE,低 8 位存入寄存器 A。

#### 字操作高字节缓存器

|        | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| HIBYTE | HIBYTE7 | HIBYTE6 | HIBYTE5 | HIBYTE4 | HIBYTE3 | HIBYTE2 | HIBYTE1 | HIBYTE0 |

| R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 初始值    | Х       | Х       | Х       | Х       | Х       | Х       | Х       | Х       |

BIT[7:0] HIBYTE[7:0] - 字操作高字节缓存器

HIBYTE: 用于缓存通过 INDF3 访问程序存储器时所读取内容的高 8 位。

### 程序指针计数器低字节

|     | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| PCL | PC7    | PC6    | PC5    | PC4    | PC3    | PC2    | PC1    | PC0    |

| R/W | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] PC[7:0] - 程序指针计数器低 8 位

### 程序指针计数器 (PC) 有以下几种操作模式:

♦ 顺序运行指令: PC = PC + 1;

令 程序跳转指令 GOTO/CALL: PC = 指令码低 13 位;

◇ 返回指令 RETIE/RETURN/RETAI: PC = 堆栈栈顶 (TOS);

### 对 PCL 操作指令:

*晟矽微电* 25/127

→ 对 PCL 操作的加法指令: PC = (PC[12:0]+ALU[7:0]);

→ 对 PCL 操作的其他指令: PC = (PC[12:8]:ALU[7:0](ALU 运算结果));

#### CPU 状态寄存器

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| PFLAG | -      | -      | -      | -      | -      | Z      | DC     | С      |

| R/W   | -      | -      | -      | -      | -      | R/W    | R/W    | R/W    |

| 初始值   | -      | -      | -      | -      | -      | Х      | Х      | Х      |

BIT[2] Z - 零标志位

0: 算术或逻辑运算的结果不为零;

1: 算术或逻辑运算的结果为零;

BIT[1] DC - 半字节进位/借位标志位

0: 加法运算中半字节无进位;减法运算中半字节有借位;

1: 加法运算中半字节有进位;减法运算中半字节无借位;

BIT[0] C - 进位/借位标志位

0: 加法运算中无进位;减法运算中有借位;移位操作中移出位为0;

1: 加法运算中有进位;减法运算中无借位;移位操作中移出位为1;

#### 杂项控制寄存器

|     | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| MCR | GIE    |        | ТО     | PD     | INT1M1 | INT1M0 | INT0M1 | INT0M0 |

| R/W | R/W    |        | R      | R      | R/W    | R/W    | R/W    | R/W    |

| 初始值 | 0      | -      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7] GIE - 中断总使能位

0: 屏蔽所有中断;

1: 由相应的中断使能位决定 CPU 是否响应中断源所触发的中断;

BIT[5] TO - 看门狗溢出标志位

0: 上电复位,或已执行 CLRWDT/STOP 指令;

1: 发生 WDT 溢出;

*晟矽微电* 26/127

BIT[4] PD - 进入低功耗模式标志位

0: 上电复位,或已执行 CLRWDT 指令;

1: 已执行 STOP 指令;

###

| INT1M[1:0] | INT1 触发方式 |  |  |

|------------|-----------|--|--|

| 00         | 上升沿触发     |  |  |

| 01         | 下降沿触发     |  |  |

| 1X         | 电平变化触发    |  |  |

### BIT[1:0] INTOM[1:0] - 外部中断 INTO 触发方式选择位

| INT0M[1:0] | INTO 触发方式 |

|------------|-----------|

| 00         | 上升沿触发     |

| 01         | 下降沿触发     |

| 1X         | 电平变化触发    |

### 3.6 用户配置字

芯片为保证系统正常工作,会将关键模块的配置信息预先存储于单独的存储器区域内,在上电或其 他复位发生后将配置信息载入寄存器中,通过寄存器控制关键模块的工作状态。该部分存储器中用户可 选的内容即为用户配置字,可在烧录用户程序代码时进行配置与烧录。

### 芯片的用户配置字,定义如下:

| 符号      |                                        | 功能说明           |                |  |  |  |  |  |

|---------|----------------------------------------|----------------|----------------|--|--|--|--|--|

|         | 高频时钟下 Fcpu 分频选择                        | :              |                |  |  |  |  |  |

| FCPUS   | Fcpu=Fhosc/2;                          | Fcpu=Fhosc/4;  | Fcpu=Fhosc/8;  |  |  |  |  |  |

|         | Fcpu=Fhosc/16;                         | Fcpu=Fhosc/32; | Fcpu=Fhosc/64; |  |  |  |  |  |

| DCTEN   | RST 外部复位端口设置:                          |                |                |  |  |  |  |  |

| RSTEN   | P14 为外部复位脚; P14 为输入/输出脚;               |                |                |  |  |  |  |  |

| LVRMD   | LVR 模式设置:                              |                |                |  |  |  |  |  |

| LVRMD   | LVR 始终开启;                              | LVR 在运行模式下开启   | ,在低功耗模式下关闭;    |  |  |  |  |  |

| 17/D//C | LVR 复位电压选择:(LVR 电压应满足由 Fcpu 决定的工作电压特性) |                |                |  |  |  |  |  |

| LVRVS   | 1.8V; 2.0V; 2.7V; 4.1V;                |                |                |  |  |  |  |  |

| WDTM    | WDT 模式设置:                              |                |                |  |  |  |  |  |

*晟矽微电* 27/127

|             | WDT 始终关闭;                   |                |  |  |  |  |  |  |

|-------------|-----------------------------|----------------|--|--|--|--|--|--|

|             | WDT 在运行模式下开启,在低功耗模式下关闭;     |                |  |  |  |  |  |  |

|             | WDT 始终开启;                   |                |  |  |  |  |  |  |

| WDTT        | WDT 溢出时间(典型值)选择:            |                |  |  |  |  |  |  |

| WDII        | 16ms; 64ms; 256ms; 10       | 024ms;         |  |  |  |  |  |  |

| CMTVC       | 端口施密特阈值选择:                  |                |  |  |  |  |  |  |

| SMTVS       | 2.0V/0.8V;                  | 0.8VDD/0.2VDD; |  |  |  |  |  |  |

| CDDC        | 端口输出驱动管开关速度选择(不包括 P20/P21): |                |  |  |  |  |  |  |

| SPDS        | 高速输出;                       | 低速输出;          |  |  |  |  |  |  |

| ENCD        | 程序代码加密设置:                   |                |  |  |  |  |  |  |

| ENCR        | 程序代码加密;                     | 程序代码不加密;       |  |  |  |  |  |  |

|             | PCK0/PDT0 编程扩展设置:           |                |  |  |  |  |  |  |

| DBGPIN0     | 端口在复位时固定为编程端口,复位完成后固定为通用端口; |                |  |  |  |  |  |  |

|             | 可通过寄存器位将端口切换为编程端口或通用端口;     |                |  |  |  |  |  |  |

|             | PCK1/PDT1 编程扩展设置:           |                |  |  |  |  |  |  |

| DBGPIN1     | 端口在复位时固定为编程端口,复位完成后固定为通用端口; |                |  |  |  |  |  |  |

|             | 可通过寄存器位将端口切换                | 为编程端口或通用端口;    |  |  |  |  |  |  |

| <del></del> |                             |                |  |  |  |  |  |  |

*晟矽微电* 28/127

### 4 系统时钟

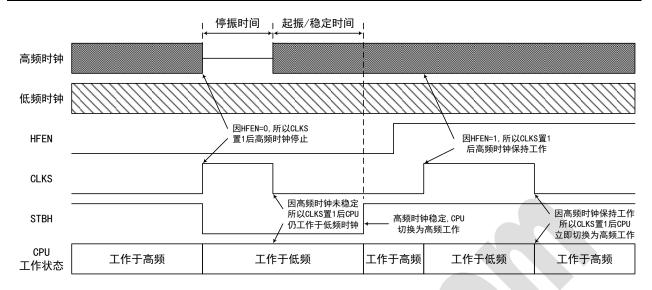

芯片内部电路均在系统高频时钟 Fhosc 或系统低频时钟 Flosc 下工作,系统及部分外设模块的时钟源还可在 Fhosc 和 Flosc 之间切换。

系统高频时钟 Fhosc 固定为内部高频 RC 振荡器 HIRC(32MHz)时钟 Fhire;系统低频时钟 Flosc 固定为内部低频 RC 振荡器 LIRC(32KHz)时钟 Flire。

CPU 的时钟源可在系统高频时钟 Fhosc 和系统低频时钟 Flosc 之间切换。Fhosc 下 CPU 的时钟频率 Fcpu 通过配置字 FCPUS 选择;Flosc 下 Fcpu 则固定为 Flosc 的 2 分频。

WDT(看门狗)电路的时钟源固定为内部低频 RC 振荡器 LIRC。

#### 系统时钟示意图

### 4.1 内部高频 RC 振荡器

芯片内置 1 个振荡频率为 32MHz 的高精度 HIRC 振荡器,可用作系统高频时钟源。

### 4.2 内部低频 RC 振荡器

芯片内置 1 个振荡频率典型值为 32KHz 的 LIRC 振荡器,可用作系统低频时钟源,也用于系统上电

*晟矽微电* 29/127

延时控制、看门狗定时器(WDT)等电路。

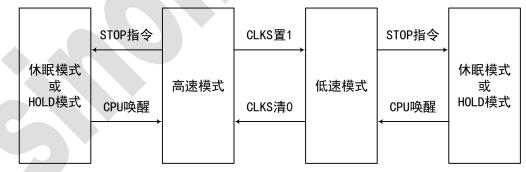

### 4.3 系统工作模式

芯片支持高速模式、低速模式、HOLD1模式、HOLD2模式和休眠模式等多种系统工作模式。

| 工作模式   | 模式切换条件                             | 系统工作状态                   |  |  |  |

|--------|------------------------------------|--------------------------|--|--|--|

|        | 任意模式下,系统复位                         |                          |  |  |  |

| 高速     | 低速模式下,CLKS 清 0                     | CPU 高速运行,高/低频时钟源均工作      |  |  |  |

|        | HOLD1/HOLD2/休眠模式下,CPU 唤醒(@CLKS=0)  |                          |  |  |  |

| /rt \= | 高速模式下,CLKS 置 1                     | CPU 低速运行,低频时钟源工作,高频时钟源由使 |  |  |  |

| 低速     | HOLD1/HOLD2/休眠模式下,CPU 唤醒(@CLKS=1)  | 能位 HFEN 决定               |  |  |  |

| HOLD1  | 高/低速模式下,执行 STOP 指令(@HFEN=1)        | CPU 暂停,高频时钟源工作,低频时钟源由使能位 |  |  |  |

| HOLDI  | 向/瓜述侯式下,挽们 STOP 指マ(@nrcin-1)       | LFEN 决定                  |  |  |  |

| HOLD2  | 高/低速模式下,执行 STOP 指令(@HFEN=0,LFEN=1) | CPU 暂停,高频时钟源停止,低频时钟源工作   |  |  |  |

| 休眠     | 高/低速模式下,执行 STOP 指令(@HFEN=0,LFEN=0) | CPU 暂停,高/低频时钟源均停止        |  |  |  |

注: WDT 时钟源为 LIRC, WDT 开启时 LIRC 将一直工作而不受系统工作模式影响。

### 工作模式切换示意图

高低频时钟切换时序图

*晟矽微电* 30/127

### 振荡器模式寄存器

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| OSCMR | -      | -      | STBL   | STBH   | -      | CLKS   | LFEN   | HFEN   |

| R/W   | -      | -      | R      | R      |        | R/W    | R/W    | R/W    |

| 初始值   | -      | -      | Х      | 1      | -      | 0      | 0      | 0      |

BIT[5] STBL - 低频时钟源振荡状态标志位

0: 低频时钟源停振或未稳定;

1: 低频时钟源已稳定振荡;

BIT[4] STBH - 高频时钟源振荡状态标志位

0: 高频时钟源停振或未稳定;

1: 高频时钟源已稳定振荡;

BIT[2] CLKS - CPU 时钟源选择位

0: 系统高频时钟作为 CPU 时钟源;

1: 系统低频时钟作为 CPU 时钟源;

BIT[1] LFEN - 低频时钟源使能位

0: 在休眠/HOLD 模式下, 低频时钟源暂停工作;

1: 低频时钟源始终工作;

BIT[0] HFEN - 高频时钟源使能位

0: 在低速/休眠/HOLD 模式下, 高频时钟源暂停工作;

*晟矽微电* 31/127

### 1: 高频时钟源始终工作;

### 4.4 低功耗模式

芯片的高速模式、低速模式为运行模式,而休眠模式、HOLD1模式、HOLD2模式则为低功耗模式。

执行 STOP 指令可使系统进入低功耗模式,同时对系统会产生以下影响:

- ◆ CPU 停止运行;

- ◇ 根据不同模式停止相应时钟源的振荡;

- ♦ RAM 内容保持不变;

- ◇ 所有的输入/输出端口保持原有状态;

- ◇ 定时器若其时钟源未停止,则可继续工作;

### 以下情况可使系统退出低功耗模式:

- ◇ 芯片复位;

- ◆ WDT 溢出(若低功耗模式下 WDT 及其时钟源保持继续工作);

- ◆ 外部中断请求发生(若有外部中断功能并有效);

- ◆ 定时器中断请求发生(若低功耗模式下定时器及其时钟源保持继续工作);

- ◆ 键盘中断请求发生(若有键盘中断功能并有效);

- ◇ 比较器 CMP 中断请求发生(若低功耗模式下比较器保持继续工作);

- ♦ UART 接收完成中断请求发生(若低功耗模式下 UART 及其时钟源保持继续工作);

- ♦ IIC 从机模式下检测到总线发送的地址帧或数据帧信号(异步采样方式);

#### 注:

- 1、 低功耗模式下触发中断请求时,若对应的中断使能位关闭,则不会退出低功耗模式;若对应的中断使能位开启 而中断总使能位关闭,则仅唤醒 CPU 执行下一条指令;若对应的中断使能位和中断总使能位均开启,则唤醒 CPU 后将执行中断服务程序;

- 2、 未使用或未封出的引脚,应将其对应的 I/O 端口设置为输出、输入上拉或输入下拉等稳定状态,以免因引脚浮空而产生漏电流或非预期的中断唤醒;

*晟矽微电* 32/127

### 5 复位

### 5.1 复位条件

芯片共有如下几种复位方式:

- ◆ 上电复位 POR;

- ◆ 低电压复位 LVR;

- ♦ 外部复位;

- ♦ WDT 看门狗复位;

任何一种复位发生后,系统进入复位状态,执行初始化操作并重置 SFR 为复位初始值;复位条件解除后,系统退出复位状态,在保持一定时间的复位延时(典型值约为 16ms)以等待电路稳定后,CPU 重新从程序存储器 0000H 地址处开始运行。

注:若应用系统在上电或掉电回升时芯片的 VDD 电压上升较慢,则应在复位后 CPU 开始工作时先进行软件延时,以确保芯片开始工作时 VDD 电压已稳定在 Fcpu 对应的工作电压范围内。

### 5.2 上电复位

芯片的上电复位电路可以适应系统快速上电或慢速上电等情况,即使上电过程中发生电源电压抖动的情况也能保证系统可靠的复位。

### 上电复位过程主要包括以下几个步骤:

- (1) 检测系统电源电压,等待电压高于上电复位电压 Vpor 并保持稳定;

- (2) 若 LVR 功能开启,则需等待电压高于低电压复位电压 VLVR 并保持稳定;

- (3) 若有外部复位功能并已开启,则需等待外部复位引脚电压高于 Vih;

- (4) 初始化所有初始值确定的寄存器;

- (5) 开启主时钟振荡器,并等待一段时间以待振荡器稳定;

- (6) 上电复位结束, CPU 开始执行指令;

*晟矽微电* 33/127

### 5.3 外部复位

芯片的外部复位功能可通过配置字 RSTEN 开启,引脚设为外部复位脚即为开启外部复位功能,端口内部上拉电阻将自动使能。外部复位输入端口 RST 为施密特结构,低电平有效,即当端口输入为高电平时系统正常运行,输入为低电平时系统复位。

### 5.4 低电压复位

芯片的低电压复位电压 VLVR 可通过配置字 LVRVS 选择。LVR 检测电路具有一定的回滞特性,回滞电压约为 6%(典型值),当电源电压下降至 VLVR 时发生 LVR 复位,反之电源电压需上升至 VLVR+6%后 LVR 复位才解除。

### 5.5 看门狗复位

芯片的看门狗定时器(WDT)复位是一种对系统运行程序的保护机制。正常情况下,用户程序需定时对 WDT 执行清零操作,以避免 WDT 溢出。若发生异常情况,程序未及时清零 WDT,则芯片将因 WDT 溢出而产生看门狗复位,系统初始化后重新运行程序,从而返回受控状态。

注:低功耗模式下 CPU 暂停工作,若此时发生 WDT 溢出,则仅唤醒 CPU 而不复位芯片。

### 6 I/O 端口

### 6.1 通用 I/O 功能

芯片的输入/输出端口包括两组 8 位端口 P0、P1,和一组 2 位端口 P2。所有端口均支持施密特输入,均支持推挽输出,P14/P15 还可选开漏输出。除用作通用数字 I/O 端口外,部分端口还可复用为外部中断输入、PWM 输出、或 ADC 模拟输入等功能。

### 端口数据寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| IOP0 | P07D   | P06D   | P05D   | P04D   | P03D   | P02D   | P01D   | P00D   |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] P0nD – P0n 端口数据位(n=7-0)

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| IOP1 | P17D   | P16D   | P15D   | P14D   | P13D   | P12D   | P11D   | P10D   |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

BIT[7:0] P1nD - P1n 端口数据位(n=7-0)

|      | Bit[7]   | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|----------|--------|--------|--------|--------|--------|--------|--------|

| IOP2 | <b>(</b> |        | -      | 1      | 1      | 1      | P21D   | P20D   |

| R/W  | ·        | i      | 1      | 1      | 1      | 1      | R/W    | R/W    |

| 初始值  | -        | -      | -      | -      | -      | -      | Х      | Х      |

BIT[1:0] P2nD - P2n 端口数据位(n=1-0)

### 端口方向寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| OEP0 | P070E  | P060E  | P050E  | P040E  | P030E  | P020E  | P010E  | P000E  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P0nOE - P0n 端口输出使能位(n=7-0)

0: 端口作为输入口,读端口操作将读取端口的电平状态;

*晟矽微电* 35/127

### 1: 端口作为输出口,读端口操作将读取端口的数据位值;

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| OEP1 | P170E  | P160E  | P150E  | P140E  | P130E  | P120E  | P110E  | P100E  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P1nOE - P1n 端口输出使能位(n=7-0)

0: 端口作为输入口,读端口操作将读取端口的电平状态;

1: 端口作为输出口,读端口操作将读取端口的数据位值;

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2]     | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|------------|--------|--------|

| OEP2 | -      | -      | -      | -      | -      |            | P210E  | P200E  |

| R/W  | -      | -      | -      | -      |        |            | R/W    | R/W    |

| 初始值  | -      | -      | -      | -      | -      | <b>J</b> - | 0      | 0      |

BIT[1:0] P2nOE - P2n 端口输出使能位(n=1-0)

0: 端口作为输入口,读端口操作将读取端口的电平状态;

1: 端口作为输出口,读端口操作将读取端口的数据位值;

### 6.2 内部上/下拉电阻

所有端口均具有内部上拉和下拉电阻,且均可单独控制其上/下拉电阻在端口处于输入状态(或端口数字 I/O 功能关闭)时是否有效。端口处于输出状态时,上/下拉电阻及其控制位无效。

#### 上拉电阻控制寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PUP0 | P07PU  | P06PU  | P05PU  | P04PU  | P03PU  | P02PU  | P01PU  | P00PU  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P0nPU - P0n 端口上拉电阻控制位(n=7-0)

0: 端口内部上拉电阻无效;

1: 端口内部上拉电阻有效;

*晟矽微电* 36/127

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PUP1 | P17PU  | P16PU  | P15PU  | P14PU  | P13PU  | P12PU  | P11PU  | P10PU  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P1nPU - P1n 端口上拉电阻控制位(n=7-0)

3. 端口内部上拉电阻无效;1. 端口内部上拉电阻有效;

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PUP2 | -      | -      | -      | -      | -      | -      | P21PU  | P20PU  |

| R/W  | -      | -      | -      | -      | -      |        | R/W    | R/W    |

| 初始值  | -      | -      | -      | -      | -      | -      | 0      | 0      |

BIT[1:0] P2nPU - P2n 端口上拉电阻控制位(n=1-0)

0: 端口内部上拉电阻无效;

1: 端口内部上拉电阻有效;

### 下拉电阻控制寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PDP0 | P07PD  | P06PD  | P05PD  | P04PD  | P03PD  | P02PD  | P01PD  | P00PD  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P0nPD - P0n 端口下拉电阻控制位(n=7-0)

0: 端口内部下拉电阻无效;

1: 端口内部下拉电阻有效;

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PDP1 | P17PD  | P16PD  | P15PD  | P14PD  | P13PD  | P12PD  | P11PD  | P10PD  |

| R/W  | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P1nPD - P1n 端口下拉电阻控制位(n=7-0)

0: 端口内部下拉电阻无效;

1: 端口内部下拉电阻有效;

|  | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|--|--------|--------|--------|--------|--------|--------|--------|--------|

|--|--------|--------|--------|--------|--------|--------|--------|--------|

*晟矽微电* 37/127

| PDP2 | - | - | - | - | - | - | P21PD | P20PD |

|------|---|---|---|---|---|---|-------|-------|

| R/W  | - | - | - | - | - | - | R/W   | R/W   |

| 初始值  | - | - | - | - | - | - | 0     | 0     |

BIT[1:0] P2nPD - P2n 端口下拉电阻控制位(n=1-0)

3. 端口内部下拉电阻无效;1. 端口内部下拉电阻有效;

## 6.3 端口模式控制

部分端口除可作为数字端口外,还可复用为模拟端口。端口输入或输出模拟信号时,若数字 I/O 功能同时开启,则会产生漏电流,可通过端口数模控制寄存器关闭端口的数字 I/O 功能(内部上/下拉电阻及其控制位不受影响)。

### 端口数模控制寄存器

|        | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| P0ADCR | P07DC  | P06DC  | P05DC  | P04DC  | P03DC  | P02DC  | P01DC  | P00DC  |

| R/W    |

| 初始值    | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P0nDC - P0n 端口数字功能控制位(n=7-0)

0: 使能端口的数字 I/O 功能;1: 关闭端口的数字 I/O 功能;

|        | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| P1ADCR | P17DC  | P16DC  | P15DC  | P14DC  | P13DC  | P12DC  | P11DC  | P10DC  |

| R/W    |

| 初始值    | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[7:0] P1nDC - P1n 端口数字功能控制位(n=7-0)

0: 使能端口的数字 I/O 功能;1: 关闭端口的数字 I/O 功能;

用作数字输出口时,P14/P15 可选择推挽输出或开漏输出。当端口为推挽输出、或开漏输出低时,

*晟矽微电* 38/127

输入通路保持连接; 而当端口开漏输出高时, 输入通路将自动关断。

### 端口模式控制寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| PMOD | -      | -      | -      | -      | -      | -      | P150D  | P140D  |

| R/W  | -      | -      | -      | -      | -      | -      | R/W    | R/W    |

| 初始值  | -      | -      | -      | -      | -      | -      | 0      | 0      |

BIT[1] P15OD - P15 端口开漏输出控制位

0: 端口输出时为推挽输出; 1: 端口输出时为开漏输出;

BIT[0] P14OD - P14 端口开漏输出控制位

0: 端口输出时为推挽输出;1: 端口输出时为开漏输出;

# 6.4 端口驱动控制

P20/P21 为大电流端口且输出电流 4 级可选。

### 端口驱动控制寄存器

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| DRVCR | -      | -      | PDRV1  | PDRV0  | PDLY1  | PDLY0  | PSPD1  | PSPD0  |

| R/W   | -      | -      | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | -      | -      | 0      | 0      | 0      | 0      | 0      | 0      |

BIT[5:4] PDRV[1:0] - P20/P21 端口输出驱动电流选择位

| PDRV[1:0] | P20/P21 输出驱动电流 |

|-----------|----------------|

| 00        | 25mA           |

| 01        | 50mA           |

| 10        | 75mA           |

| 11        | 100mA          |

BIT[3:2] PDLY[1:0] - P20/P21 端口驱动前级非叠时间选择位

*晟矽微电* 39/127

| PDLY[1:0] | P20/P21 驱动前级非叠时间 |

|-----------|------------------|

| 00        | 10ns             |

| 01        | 50ns             |

| 10        | 禁用               |

| 11        | 禁用               |

BIT[1:0] PSPD[1:0] - P20/P21 端口驱动管开关时间选择位

| PSPD[1:0] | P20/P21 驱动管开关时间 |

|-----------|-----------------|

| 00        | 10ns            |

| 01        | 50ns            |

| 10        | 禁用              |

| 11        | 禁用              |

# 7 可编程 RC 振荡器 PFRC

芯片内置 1 个频率可编程的高频 RC 振荡器 PFRC,输出时钟 FPFRC 仅可用作定时器时钟源。

PFRC 振荡频率可微调校准,校准值保存在 12 位微调校准寄存器 PFRCCAL 中,芯片复位后,寄存器自动加载出厂设置值,将 FPFRC 初始值调整至 32MHz。该寄存器允许通过软件进行微调,可生成一定范围内的其他频率。

#### PFRC 控制寄存器

|        | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2]      | Bit[1] | Bit[0] |

|--------|--------|--------|--------|--------|--------|-------------|--------|--------|

| PFRCCR | PFRCEN | -      | -      | -      | -      | -           | -      | -      |

| R/W    | R/W    | -      | -      | -      | -      |             | -      | -      |

| 初始值    | 0      | -      | -      | -      | -      | <b>)</b> -) | -      | -      |

BIT[7] PFRCEN - PFRC 使能位

0: 关闭 PFRC;

1: 开启 PFRC;

### PFRC 微调校准寄存器

|          | Bit[7]    | Bit[6]    | Bit[5]   | Bit[4]   | Bit[3]   | Bit[2]   | Bit[1]   | Bit[0]   |

|----------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| PFRCCALH | PFRCCAL11 | PFRCCAL10 | PFRCCAL9 | PFRCCAL8 | PFRCCAL7 | PFRCCAL6 | PFRCCAL5 | PFRCCAL4 |

| R/W      | R/W       | R/W       | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      |

| 初始值      | U         | U         | U        | U        | U        | U        | U        | U        |

BIT[7:0] PFRCCAL[11:4] - PFRC 频率微调校准位高 8 位(复位初始值为出厂设置值)

|          | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3]   | Bit[2]   | Bit[1]   | Bit[0]   |

|----------|--------|--------|--------|--------|----------|----------|----------|----------|

| PFRCCALL |        | -      | -      | -      | PFRCCAL3 | PFRCCAL2 | PFRCCAL1 | PFRCCAL0 |

| R/W      | -      | -      | -      | -      | R/W      | R/W      | R/W      | R/W      |

| 初始值      | -      | -      | -      | -      | U        | U        | U        | U        |

BIT[3:0] PFRCCAL[3:0] - PFRC 频率微调校准位低 4 位(复位初始值为出厂设置值)

注:

1、 PFRC 开启后需延时一段时间(>200μs)以待其振荡稳定,才可正常应用;

*晟矽微电* 41/127

- 2、 PFRC 最大调节范围为(32MHz -10%)—(32MHz +4%)(以实际芯片为准);

- 3、 校准位1个LSB 所调节的频率变化是非线性的,最大约为 0.2%;

- 4、 PFRCCAL 中已有出厂校准值,软件微调前应备份原值以便恢复;

*晟矽微电* 42/127

### 8 定时器 TIMER

## 8.1 看门狗定时器 WDT

看门狗定时器 WDT 的时钟源为内部低频 RC 振荡器 LIRC, WDT 溢出将复位芯片或唤醒 CPU。

可通过配置字 WDTM 设置 WDT 工作模式:选择始终开启,则 WDT 一直工作,高速/低速模式下 WDT 溢出将复位芯片,休眠/HOLD 模式下 WDT 溢出将唤醒 CPU;选择低功耗模式下关闭,则 WDT 在 休眠/HOLD 模式下自动关闭、在其他方式唤醒 CPU 后恢复工作。

执行 CLRWDT 指令或 STOP 指令将清零 WDT 计数器。

WDT 溢出时间可配置为 16ms/64ms/256ms/1024ms。

注:WDT 溢出时间为典型值,而实际值偏差较大,必须保证清 WDT 的间隔时间小于 WDT 溢出时间的 1/4。

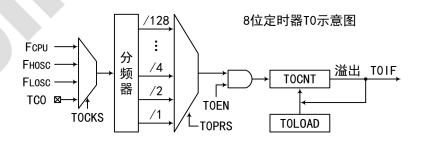

## 8.2 定时器 T0

定时器 T0 为 8 位定时/计数器,包含 1 个 8 位递减计数器、可编程预分频器、控制寄存器、8 位重载寄存器。

- ◆ 可通过预分频器设置时钟频率,可通过重载寄存器控制计数周期;

- ◇ 支持溢出中断和溢出唤醒功能;

定时器 T0,可通过寄存器位 T0CKS 选择时钟源,通过 T0PRS 选择时钟预分频比,所选时钟源通过 预分频器后产生 T0 计数器 T0CNT 的计数时钟(上升沿计数)。写 T0CNT 将清零预分频计数器,而预分 频比保持不变。

*晟矽微电* 43/127

T0EN=0 时,T0CNT 保持不变,写重载寄存器 T0LOAD 将立即载入 T0CNT; T0EN=1 时,T0CNT 递减计数,计数到 0 的时钟结束后产生溢出信号并触发中断,中断标志 T0IF 将被置 1,同时 T0 自动将 当前 T0LOAD 值载入 T0CNT 并重新开始计数。

定时器 T0 控制寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| T0CR | T0EN   | 1      | 1      | T0CKS1 | T0CKS0 | T0PRS2 | T0PRS1 | T0PRS0 |

| R/W  | R/W    | -      | -      | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | -      | -      | 0      | 0      | 0      | 0      | 0      |

BIT[7] TOEN - 定时器 TO 使能位

0: 关闭定时器 T0; 1: 开启定时器 T0;

BIT[4:3] TOCKS[1:0] - TO 时钟源选择位

| T0CKS[1:0] | T0 时钟源  |

|------------|---------|

| 00         | Fcpu    |

| 01         | FHOSC   |

| 10         | FLOSC   |

| 11         | TC0 上升沿 |

# BIT[2:0] T0PRS[2:0] - T0 时钟预分频比选择位

| T0PRS[2:0] | T0 时钟预分频比 |

|------------|-----------|

| 000        | 1:1       |

| 001        | 1:2       |

| 010        | 1:4       |

| 011        | 1:8       |

| 100        | 1:16      |

| 101        | 1:32      |

| 110        | 1:64      |

| 111        | 1:128     |

定时器 T0 计数器

*晟矽微电* 44/127

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| T0CNT | T0CNT7 | T0CNT6 | T0CNT5 | T0CNT4 | T0CNT3 | T0CNT2 | T0CNT1 | T0CNT0 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值   | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

BIT[7:0] TOCNT[7:0] - TO 计数器,为可读写的递减计数器

### 定时器 T0 重载寄存器

|        | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| T0LOAD | T0LOAD7 | T0LOAD6 | T0LOAD5 | T0LOAD4 | T0LOAD3 | T0LOAD2 | T0LOAD1 | T0LOAD0 |

| R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 初始值    | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

BIT[7:0] TOLOAD[7:0] - TO 重载寄存器,用于设置 TO 的计数周期

注: 定时器重载寄存器的值禁止为 0,否则定时器将无法正常工作。

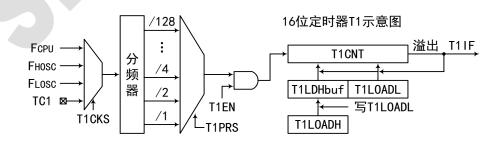

# 8.3 定时器 T1

定时器 T1 为 16 位定时/计数器,包含 1 个 16 位递减计数器、可编程预分频器、控制寄存器、16 位重载寄存器。

- ◇ 可通过预分频器设置时钟频率,可通过重载寄存器控制计数周期;

- ◆ 支持单次计时模式(触摸模式),可控制触摸模块是否进行电容充放计数;

- ◇ 支持溢出中断和溢出唤醒功能;

定时器 T1,可通过寄存器位 T1CKS 选择时钟源,通过 T1PRS 选择时钟预分频比,所选时钟源通过 预分频器后产生 T1 计数器 T1CNT 的计数时钟(上升沿计数)。写 T1CNT 将清零预分频计数器,而预分

*晟矽微电* 45/127

#### 频比保持不变。

16 位 T1CNT 的低字节 T1CNTL 配有缓冲器,读写 T1CNTL 实际为读写缓冲器中内容,T1CNTL 实际内容仅在读写 T1CNTH 时才自动与缓冲器交互,因此写 T1CNT 需先写 T1CNTL 再写 T1CNTH(硬件同时自动将缓存器内容载入 T1CNTL),而读 T1CNT 则需先读 T1CNTH(硬件同时自动将 T1CNTL 内容载入缓冲器中)再读 T1CNTL。

T1EN=0 时,T1CNT 保持不变,写重载寄存器 T1LOAD 将立即载入 T1CNT; T1EN=1 时,T1CNT 递减计数,计数到 0 的时钟结束后产生溢出信号并触发中断,中断标志 T1IF 将被置 1,同时 T1 自动将当前 T1LOAD 值载入 T1CNT 并重新开始计数。

16 位 T1LOAD 的高字节 T1LOADH 配有缓冲器(T1LDHbuf),写 T1LOADL 时会同时将 T1LOADH 内容载入该缓冲器中,因此调整 T1LOAD 值时需先写 T1LOADH 再写 T1LOADL。此时若 T1EN=0,则会同时再将[缓冲器:T1LOADL]载入 T1CNT;若 T1EN=1,则会在 T1 溢出后才将[缓冲器:T1LOADL]载入 T1CNT。

定时器 T1 在单次计时模式下,T1EN 置 1 将允许 16 位 TKM 电容充放计数器 TKCNT 计数 (需 TKEN 和 TKCON 均为 1),当 T1 溢出时,中断标志 T1IF 将被置 1,同时 T1EN 自动清 0 且 TKCNT 停止计数。

定时器 T1 控制寄存器

|      | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| T1CR | T1EN   | T1MOD  | -      | T1CKS1 | T1CKS0 | T1PRS2 | T1PRS1 | T1PRS0 |

| R/W  | R/W    | R/W    | -      | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | -      | 0      | 0      | 0      | 0      | 0      |

BIT[7] T1EN - 定时器 T1 使能位

0: 关闭定时器 T1;

1: 开启定时器 T1;

BIT[6] T1MOD - T1工作模式选择位

0: 连续定时/计数模式;

1: 单次计时模式(触摸模式);

BIT[4:3] T1CKS[1:0] - T1 时钟源选择位

| T1CKS[1:0] | T1 时钟源 |

|------------|--------|

|------------|--------|

*晟矽微电* 46/127

| 00 | Fcpu    |

|----|---------|

| 01 | FHOSC   |

| 10 | Flosc   |

| 11 | TC1 上升沿 |

## BIT[2:0] T1PRS[2:0] - T1 时钟预分频比选择位

| T1PRS[2:0] | T1 时钟预分频比 |

|------------|-----------|

| 000        | 1:1       |

| 001        | 1:2       |

| 010        | 1:4       |

| 011        | 1:8       |

| 100        | 1:16      |

| 101        | 1:32      |

| 110        | 1:64      |

| 111        | 1:128     |

### 定时器 T1 计数器

|        | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1] | Bit[0] |

|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| T1CNTH | T1CNT15 | T1CNT14 | T1CNT13 | T1CNT12 | T1CNT11 | T1CNT10 | T1CNT9 | T1CNT8 |

| R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W    | R/W    |

| 初始值    | 1       | 1       | 1       | 1       | 1       | 1       | 1      | 1      |

BIT[7:0] T1CNT[15:8] - T1 计数器高 8 位,为可读写的递减计数器

|        | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| T1CNTL | T1CNT7 | T1CNT6 | T1CNT5 | T1CNT4 | T1CNT3 | T1CNT2 | T1CNT1 | T1CNT0 |

| R/W    |

| 初始值    | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

BIT[7:0] T1CNT[7:0] - T1 计数器低 8 位,为可读写的递减计数器

### 定时器 T1 重载寄存器

|         | Bit[7]   | Bit[6]   | Bit[5]   | Bit[4]   | Bit[3]   | Bit[2]   | Bit[1]  | Bit[0]  |

|---------|----------|----------|----------|----------|----------|----------|---------|---------|

| T1LOADH | T1LOAD15 | T1LOAD14 | T1LOAD13 | T1LOAD12 | T1LOAD11 | T1LOAD10 | T1LOAD9 | T1LOAD8 |

| R/W     | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W     | R/W     |

| 初始值     | 1        | 1        | 1        | 1        | 1        | 1        | 1       | 1       |

*晟矽微电* 47/127

### BIT[7:0] T1LOAD[15:8] - T1 重载寄存器高 8 位,用于设置 T1 的计数周期

|         | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| T1LOADL | T1LOAD7 | T1LOAD6 | T1LOAD5 | T1LOAD4 | T1LOAD3 | T1LOAD2 | T1LOAD1 | T1LOAD0 |

| R/W     |

| 初始值     | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

BIT[7:0] T1LOAD[7:0] - T1 重载寄存器低 8 位,用于设置 T1 的计数周期

注: 定时器重载寄存器的值禁止为 0, 否则定时器将无法正常工作。

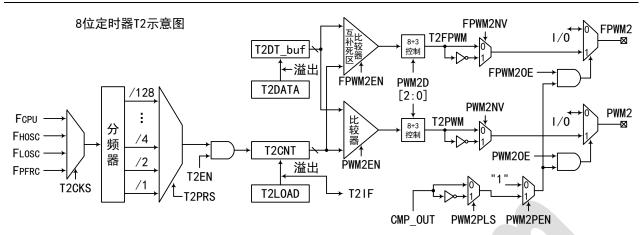

### 8.4 定时器 T2

定时器 T2 为 8 位定时器,包含 1 个 8 位递减计数器、可编程预分频器、控制寄存器、8 位重载寄存器和 8 位比较寄存器。

- ◇ 可通过预分频器设置时钟频率,可通过重载寄存器控制计数周期;

- ◆ 支持 1 对 8+3 模式的带死区互补 PWM 输出,可通过比较寄存器设置 PWM 占空比;

- ◇ 时钟源可选 FPFRC;

- ◇ 支持溢出中断和溢出唤醒功能;

- ◆ 支持 CMP 输出信号 CMP OUT 高/低电平的输出保护功能;

定时器 T2,可通过寄存器位 T2CKS 选择时钟源,通过 T2PRS 选择时钟预分频比,所选时钟源通过 预分频器后产生 T2 计数器 T2CNT 的计数时钟(上升沿计数)。写 T2CNT 将清零预分频计数器,而预分 频比保持不变。

T2EN=0 时,T2CNT 保持不变,写重载寄存器 T2LOAD 将立即载入 T2CNT; T2EN=1 时,T2CNT 递减计数,计数到 0 的时钟结束后产生溢出信号并触发中断,中断标志 T2IF 将被置 1,同时 T2 自动将当前 T2LOAD 值载入 T2CNT 并重新开始计数。

*晟矽微电* 48/127

如图所示,定时器 T2 可实现 1 对互补且带死区(2 路互补信号高电平非交叠时间)控制的 PWM 功能(PWM2/FPWM2),可通过寄存器位使能或关闭 PWM 功能,并控制端口是否输出 PWM 波形。PWM2 关闭时 T2PWM 信号为低电平,FPWM2 关闭时 T2FPWM 信号为高电平。PWM2/FPWM2 使能后 T2CNT 从重载值开始递减计数直到计数溢出为一个 PWM 周期: 当计数到与比较寄存器 T2DATA 相等时,T2PWM 变为高电平(T2FPWM 提前下降沿非交叠时间变为低电平);当计数溢出时,T2PWM 变为低电平(T2FPWM 滞后上升沿非交叠时间变为高电平)。

T2DATA 配有 1 个 8 位比较缓冲器(T2DT\_buf)用于与 T2CNT 比较,PWM2 和 FPWM2 均关闭时写 T2DATA 将立即载入缓冲器中,而 PWM2 或 FPWM2 使能后写 T2DATA 则将在 T2 溢出时才载入缓冲器中。若要首个 PWM 周期和占空比准确,需先写重载寄存器和比较寄存器,再使能 PWM,最后开启定时器。

#### T2PWM 信号的占空比计算如下:

- ◇ 高电平时间 = (T2DATA) × T2CNT 计数时钟周期

- ◆ 周期(T2 溢出时间) = (T2LOAD + 1) × T2CNT 计数时钟周期

- → 占空比(高电平时间/周期) = (T2DATA) / (T2LOAD + 1)

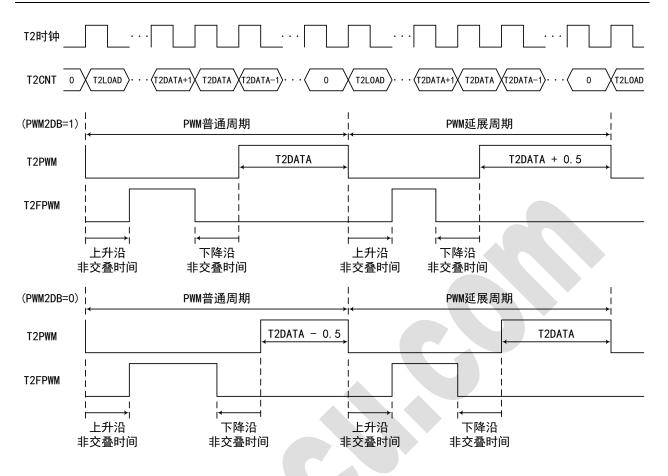

PWM2/FPWM2 支持 8+3 模式,即在普通模式 PWM 的时钟下,以每 8 个 PWM 周期作为一个大周期,其中部分周期进行占空比延展(即延展高电平时间),这些延展周期内 T2PWM 信号将比普通周期提前半个计数时钟变为高电平,即 T2PWM 高电平时间延展为(T2DATA+0.5)。

8+3 模式提高的是整体上的 PWM 占空比调节精度,而不是单个 PWM 周期的占空比调节精度。占空比延展控制位 PWM2D[2:0]决定每 8 个周期内哪几个周期为普通周期,哪几个周期为延展周期。

PWM2/FPWM2 的占空比可通过寄存器位 PWM2DB 微调半个计数时钟周期。PWM2DB=1 时,普通周期内 T2PWM 信号在计数时钟上升沿变为高电平,而延展周期内则提前半个时钟周期在时钟下降沿翻转; PWM2DB=0 时,普通周期内 T1PWM 信号滞后半个时钟周期在时钟下降沿变为高电平,而延展周期

*晟矽微电* 49/127

内则变为正常的时钟上升沿翻转。T2FPWM 信号变为低电平的时间则在叠加下降沿死区时间后进行相应 微调。

PWM2 的 8+3 模式一个大周期的占空比计算如下(需 0<T2DATA<T2LOAD):

- ◆ 高电平时间 = [(T2DATA+(PWM2DB-1)/2)×8+(PWM2D[2:0])/2] × T2CNT 计数时钟周期

- ◆ 周期 = (T2LOAD+1) × 8 × T2CNT 计数时钟周期

- ♦ 占空比(高电平时间/周期) = [T2DATA+(PWM2DB-1)/2+(PWM2D[2:0]/16)] / (T2LOAD+1)

举例说明(PWM2DB=1):

若 PWM2D[2:0]=B'000,则 8 个 PWM 周期均不进行占空比延展,一个大周期 PWM 的占空比与普通模式 PWM 的占空比一样,为[(T2DATA)/(T2LOAD+1)];

若 PWM2D[2:0]=B'101,则每 8 个 PWM 周期中的第 1、2、3、5、7 个周期(共 5 个周期)进行占空比延展,一个大周期的占空比为[(T2DATA)+(5/16)]/(T2LOAD+1);

如定时器示意图所示,PWM2/FPWM2 还支持输出保护功能,可通过 PWM2PEN 和 PWM2PLS 使能并选择 CMP 输出信号 CMP\_OUT 的高/低电平进行 PWM2/FPWM2 输出保护,当 CMP\_OUT 变为被选定的保护电平时,PWM2/FPWM2 端口将立即停止输出 PWM 波形,输出保护状态控制位 PWM2PST 自动置 1,端口转为通用 I/O 端口。只有 CMP\_OUT 恢复为解除电平后,才可通过软件清 0 控制位 PWM2PST(且仅能软件清 0)以恢复 PWM2/FPWM2 正常输出,端口将从下一个 PWM 周期开始重新输出 PWM波形。CMP\_OUT 为保护电平时,PWM2PST 无法清 0。

PWM2DB 及 8+3 模式波形示意

*晟矽微电* 50/127

注:

- 1、 应用互补 PWM 时,前后死区的总时间应小于 T2PWM 低电平时间,以确保 T2FPWM 能正常生成高电平;

- 2、 不可在 PWM 工作时调整 PWM 周期(即定时器周期)和死区时间;

- 3、8+3模式下,当PWM2DB=1时,正常周期(不延展的周期)的占空比(高电平时间)为T2DATA,而延展周期的占空比则延展半个时钟周期(即为T2DATA+0.5);当PWM2DB=0时,所有周期(包括正常周期和延展周期)的占空比均缩减半个时钟周期;

- 4、 若 T2PWM 或 T2FPWM 在 PWM2DB 为 1 时高电平时间仅为 1 个时钟周期,则 PWM2DB 清 0 操作并不会将高电平时间缩减为半个时钟周期;

- 5、 因 FCPU 的占空比不为 50%,所以当 PWM 计数时钟为 FCPU 的 1 分频时,微调功能的翻转延迟并不正好为半个时钟周期,而是延迟为 FCPU 的高电平时间;

定时器 T2 控制寄存器

|      | Bit[7] | Bit[6] | Bit[5]  | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|------|--------|--------|---------|--------|--------|--------|--------|--------|

| T2CR | T2EN   | PWM2EN | FPWM2EN | T2CKS1 | T2CKS0 | T2PRS2 | T2PRS1 | T2PRS0 |

| R/W  | R/W    | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    |

| 初始值  | 0      | 0      | 0       | 0      | 0      | 0      | 0      | 0      |

*晟矽微电* 51/127

BIT[7] T2EN - 定时器 T2 使能位

0: 关闭定时器 T2;1: 开启定时器 T2;

BIT[6] PWM2EN - PWM2 使能位

0: 关闭 PWM2 功能;1: 使能 PWM2 功能;

BIT[5] FPWM2EN - FPWM2 使能位

0: 关闭 FPWM2 功能;1: 使能 FPWM2 功能;

BIT[4:3] T2CKS[1:0] - T2 时钟源选择位

| T2CKS[1:0] | T2 时钟源 |  |  |

|------------|--------|--|--|

| 00         | Fcpu   |  |  |

| 01         | Fhosc  |  |  |

| 10         | FLOSC  |  |  |

| 11         | Fpfrc  |  |  |

## BIT[2:0] T2PRS[2:0] - T2 时钟预分频比选择位

| T2PRS[2:0] | T2 时钟预分频比 |  |  |  |

|------------|-----------|--|--|--|

| 000        | 1:1       |  |  |  |

| 001        | 1:2       |  |  |  |

| 010        | 1:4       |  |  |  |

| 011        | 1:8       |  |  |  |

| 100        | 1:16      |  |  |  |

| 101        | 1:32      |  |  |  |

| 110        | 1:64      |  |  |  |

| 111        | 1:128     |  |  |  |

### 定时器 T2 计数器

|       | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| T2CNT | T2CNT7 | T2CNT6 | T2CNT5 | T2CNT4 | T2CNT3 | T2CNT2 | T2CNT1 | T2CNT0 |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

*晟矽微电* 52/127

| _ |             |   |   |   |   |   |   |   |   |

|---|-------------|---|---|---|---|---|---|---|---|

|   | 初始值         | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|   | םן נול נגוי | _ |   |   |   |   |   |   |   |

BIT[7:0] T2CNT[7:0] - T2 计数器,为可读写的递减计数器

### 定时器 T2 重载寄存器

|        | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| T2LOAD | T2LOAD7 | T2LOAD6 | T2LOAD5 | T2LOAD4 | T2LOAD3 | T2LOAD2 | T2LOAD1 | T2LOAD0 |

| R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 初始值    | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

BIT[7:0] T2LOAD[7:0] - T2 重载寄存器,用于设置 T2 的计数周期

注: 定时器重载寄存器的值禁止为 0, 否则定时器将无法正常工作。

### 定时器 T2 比较寄存器

|        | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| T2DATA | T2DATA7 | T2DATA6 | T2DATA5 | T2DATA4 | T2DATA3 | T2DATA2 | T2DATA1 | T2DATA0 |

| R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 初始值    | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

BIT[7:0] T2DATA[7:0] - T2 比较寄存器,用于设置 PWM2 的占空比

#### PWM2 控制寄存器

|         | Bit[7]  | Bit[6]  | Bit[5]  | Bit[4] | Bit[3]  | Bit[2]  | Bit[1] | Bit[0] |

|---------|---------|---------|---------|--------|---------|---------|--------|--------|

| PWM2CR0 | PWM2PEN | PWM2PLS | PWM2PST | -      | FPWM2NV | FPWM2OE | PWM2NV | PWM2OE |

| R/W     | R/W     | R/W     | R/W     | -      | R/W     | R/W     | R/W    | R/W    |

| 初始值     | 0       | 0       | 0       | -      | 0       | 0       | 0      | 0      |

BIT[7] PWM2PEN – PWM2/FPWM2 输出保护使能位

0: 禁止 CMP\_OUT 进行 PWM2/FPWM2 输出保护;

1: 允许 CMP\_OUT 进行 PWM2/FPWM2 输出保护;

BIT[6] PWM2PLS - CMP 输出保护电平选择位

0: CMP\_OUT 低电平时进行 PWM2/FPWM2 输出保护,高电平时允许解除输出保护;

1: CMP\_OUT 高电平时进行 PWM2/FPWM2 输出保护,低电平时允许解除输出保护;

BIT[6] PWM2PST - PWM2/FPWM2 输出保护状态控制位

*晟矽微电* 53/127

0: PWM2/FPWM2 正常输出中,输出保护触发后自动置1;

1: PWM2/FPWM2 输出保护中,写 0 恢复正常输出(需 CMP\_OUT 允许解除输出保护);

BIT[3] FPWM2NV - FPWM2 端口输出取反控制位

0: 端口输出正向波形;

1: 端口对电平取反后输出;

BIT[2] FPWM2OE - FPWM2 端口输出使能位

0: 禁止端口输出脉宽调制波形;

1: 允许端口输出脉宽调制波形;

BIT[1] PWM2NV - PWM2 端口输出取反控制位

0: 端口输出正向波形;

1: 端口对电平取反后输出;

BIT[0] PWM2OE - PWM2 端口输出使能位

0: 禁止端口输出脉宽调制波形;

1: 允许端口输出脉宽调制波形;

|         | Bit[7] | Bit[6] | Bit[5]  | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|---------|--------|--------|---------|---------|---------|---------|---------|---------|

| PWM2CR1 | -      | -      | FPWM2E5 | FPWM2E4 | FPWM2E3 | FPWM2E2 | FPWM2E1 | FPWM2E0 |

| R/W     | - (    | -      | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 初始值     |        |        | 0       | 0       | 0       | 0       | 0       | 0       |

# BIT[5:0] FPWM2E[5:0] - T2FPWM 上升/下降沿非交叠时间选择位

| FPWM2E[5:0] | 上升沿非交叠时间   | 下降沿非交叠时间   |

|-------------|------------|------------|

| 00 0000     | 1 个计数时钟周期  | 1 个计数时钟周期  |

| 00 0001     | 2 个计数时钟周期  | 2 个计数时钟周期  |

|             |            |            |

|             |            |            |

| 11 1110     | 63 个计数时钟周期 | 63 个计数时钟周期 |

|         | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| PWM2CR2 | -      | -      | -      | -      | PWM2DB | PWM2D2 | PWM2D1 | PWM2D0 |

| R/W     | -      | -      | -      | -      | R/W    | R/W    | R/W    | R/W    |

*晟矽微电* 54/127

| 初始值 | - | - | - | - | 1 | 0 | 0 | 0 |

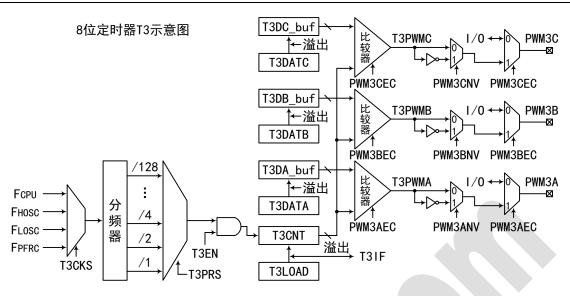

|-----|---|---|---|---|---|---|---|---|